# Programmable Controller

MELSEG Q series MELSEG L series

# MELSEC-Q/L Programming Manual (MELSAP-L)

### **SAFETY PRECAUTIONS**

Before using MELSEC-Q or -L series programmable controllers, please read the manuals included with each product and the relevant manuals introduced in those manuals carefully, and pay full attention to safety to handle the product correctly. Make sure that the end users read the manuals included with each product, and keep the manuals in a safe place for future reference.

### CONDITIONS OF USE FOR THE PRODUCT

- (1) Mitsubishi programmable controller ("the PRODUCT") shall be used in conditions;

- i) where any problem, fault or failure occurring in the PRODUCT, if any, shall not lead to any major or serious accident; and

- ii) where the backup and fail-safe function are systematically or automatically provided outside of the PRODUCT for the case of any problem, fault or failure occurring in the PRODUCT.

- (2) The PRODUCT has been designed and manufactured for the purpose of being used in general industries.

MITSUBISHI SHALL HAVE NO RESPONSIBILITY OR LIABILITY (INCLUDING, BUT NOT LIMITED TO ANY AND ALL RESPONSIBILITY OR LIABILITY BASED ON CONTRACT, WARRANTY, TORT, PRODUCT LIABILITY) FOR ANY INJURY OR DEATH TO PERSONS OR LOSS OR DAMAGE TO PROPERTY CAUSED BY the PRODUCT THAT ARE OPERATED OR USED IN APPLICATION NOT INTENDED OR EXCLUDED BY INSTRUCTIONS, PRECAUTIONS, OR WARNING CONTAINED IN MITSUBISHI'S USER, INSTRUCTION AND/OR SAFETY MANUALS, TECHNICAL BULLETINS AND GUIDELINES FOR the PRODUCT.

("Prohibited Application")

Prohibited Applications include, but not limited to, the use of the PRODUCT in;

- Nuclear Power Plants and any other power plants operated by Power companies, and/or any other cases in which the public could be affected if any problem or fault occurs in the PRODUCT.

- Railway companies or Public service purposes, and/or any other cases in which establishment of a special quality assurance system is required by the Purchaser or End User.

- Aircraft or Aerospace, Medical applications, Train equipment, transport equipment such as Elevator and Escalator, Incineration and Fuel devices, Vehicles, Manned transportation, Equipment for Recreation and Amusement, and Safety devices, handling of Nuclear or Hazardous Materials or Chemicals, Mining and Drilling, and/or other applications where there is a significant risk of injury to the public or property.

Notwithstanding the above, restrictions Mitsubishi may in its sole discretion, authorize use of the PRODUCT in one or more of the Prohibited Applications, provided that the usage of the PRODUCT is limited only for the specific applications agreed to by Mitsubishi and provided further that no special quality assurance or fail-safe, redundant or other safety features which exceed the general specifications of the PRODUCTs are required. For details, please contact the Mitsubishi representative in your region.

### INTRODUCTION

Thank you for purchasing the Mitsubishi Electric MELSEC-Q/L series programmable controllers.

Before using the product, please read this manual carefully and develop familiarity with the functions and performance of the MELSEC-Q/L series programmable controllers to handle the product correctly.

When applying the program examples provided in this manual to an actual system, ensure the applicability and confirm that it will not cause system control problems.

Please make sure that the end users read this manual.

## **CONTENTS**

| SAFI | ETY PRECAUTIONS                                                                       | 1  |

|------|---------------------------------------------------------------------------------------|----|

| CON  | IDITIONS OF USE FOR THE PRODUCT                                                       | 1  |

|      | RODUCTION                                                                             |    |

|      | EVANT MANUALS                                                                         |    |

|      | MS                                                                                    |    |

|      |                                                                                       |    |

| CHA  | APTER 1 GENERAL DESCRIPTION                                                           | 7  |

| 1.1  | Description of SFC Program                                                            |    |

| 1.2  | SFC (MELSAP-L) Features                                                               |    |

| 1.2  | or o (MELOAI -E) routuros                                                             |    |

| CHA  | APTER 2 SYSTEM CONFIGURATION                                                          | 17 |

| 2.1  | Applicable CPU Modules                                                                | 17 |

| 2.2  | Peripheral Devices for SFC Programs                                                   | 18 |

|      |                                                                                       |    |

| CHA  | APTER 3 SPECIFICATIONS                                                                | 19 |

| 3.1  | Performance Specifications Related to SFC Programs                                    | 19 |

| 3.2  | Device List                                                                           | 23 |

| 3.3  | Processing Time                                                                       | 30 |

|      | Processing time for SFC program                                                       |    |

|      | Processing time for S(P).SFCSCOMR instruction and S(P).SFCTCOMR instruction           |    |

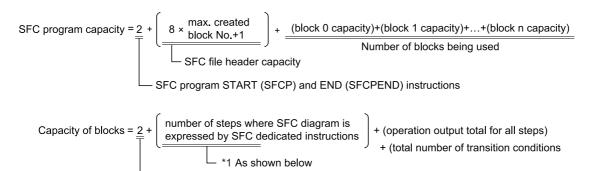

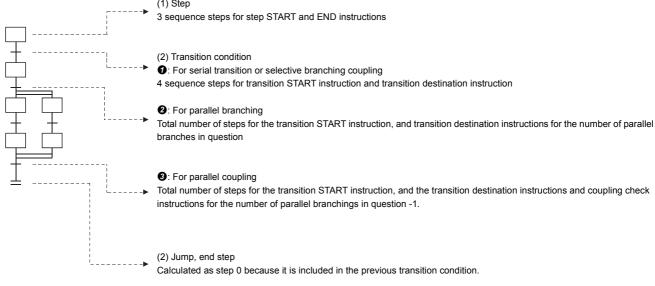

| 3.4  | Calculating the SFC Program Capacity                                                  |    |

|      | Method for calculating the SFC program capacity                                       |    |

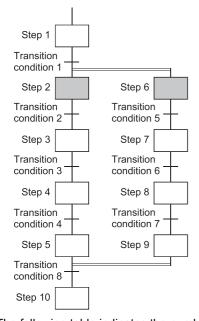

|      | Number of steps required for expressing the SFC diagram as SFC dedicated instructions |    |

|      |                                                                                       |    |

| CHA  | APTER 4 SFC PROGRAM CONFIGURATION                                                     | 38 |

| 4.1  | List of SFC Diagram Symbols                                                           | 39 |

| 4.2  | Steps                                                                                 |    |

|      | Step (without step attribute).                                                        |    |

|      | Initial step                                                                          |    |

|      | Dummy step                                                                            |    |

|      | Coil HOLD step                                                                        |    |

|      | Operation HOLD step (without transition check)                                        |    |

|      |                                                                                       |    |

|      | Operation HOLD step (with transition check)                                           |    |

|      | Reset step                                                                            |    |

|      | Block START step (with END check).                                                    |    |

|      | Block START step (without END check)                                                  |    |

|      | End step                                                                              |    |

|      | Instructions that cannot be used with operation outputs                               |    |

| 4.3  | Transition                                                                            |    |

|      | Serial transition                                                                     | 58 |

|      | Selection transition                                                                  | 60 |

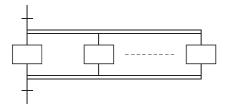

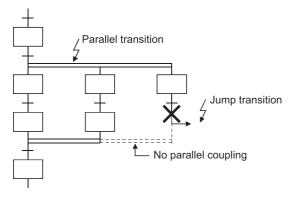

|      | Parallel transition                                                                   | 63 |

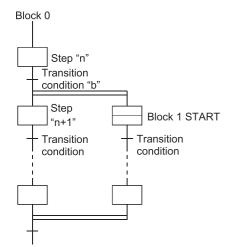

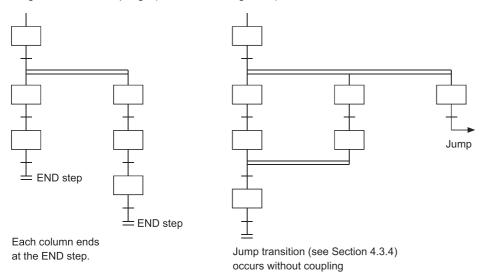

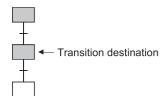

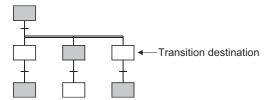

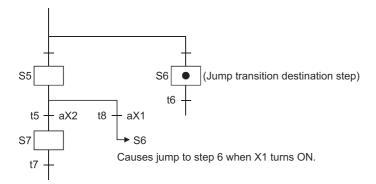

|      | Jump transition                                                                       |    |

|      | Precautions for creating operation output (step)/transition condition programs        | 68 |

| 4.4  | Controlling SFC Programs by Instructions (SFC Control Instructions)                   | 72 |

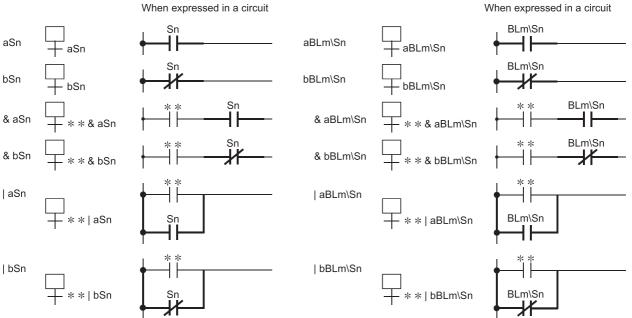

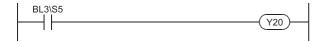

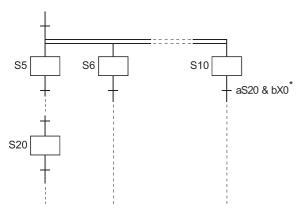

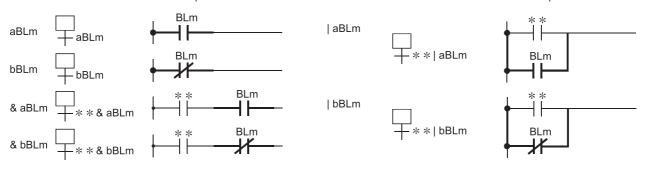

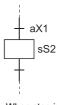

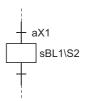

|      | Step operation status check instructions (a, b, &a, &b,  a,  b) [Sn/BLm\Sn]           | 76 |

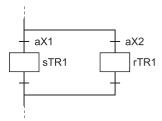

|      | Forced transition check instruction (a, b, &a, &b,  a,  b) [TRn/BLm\TRn]              | 79 |

|      | Block operation status check instruction (a. b. &a. &b. Ia. Ib) [BLm]                 | 82 |

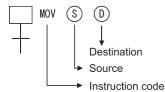

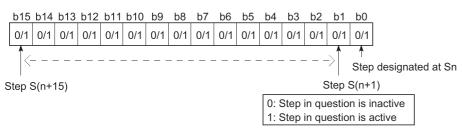

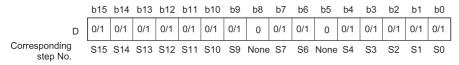

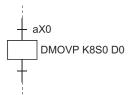

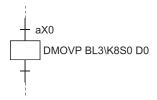

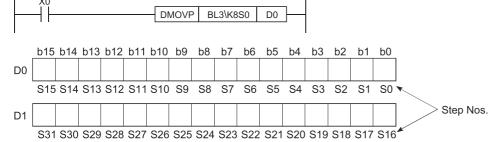

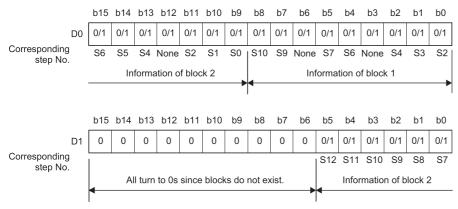

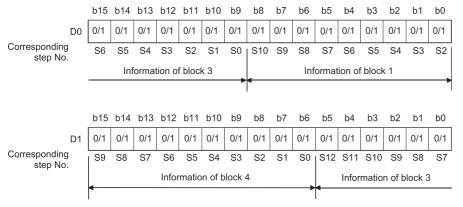

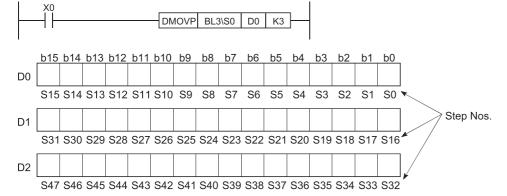

|                                 | Active step batch readout (MOV and DMOV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

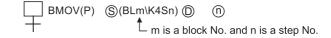

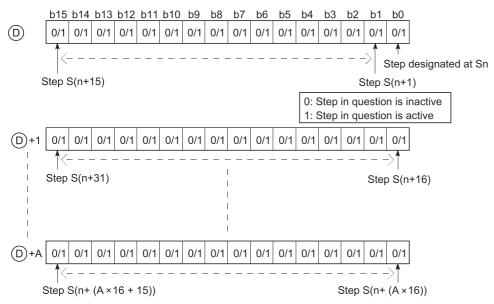

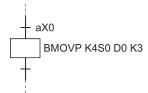

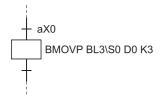

|                                 | Active step batch readout (BMOV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

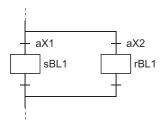

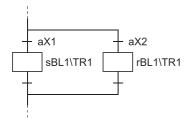

|                                 | Block START & END instructions (s, r) [BLm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90                       |

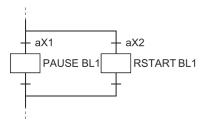

|                                 | Block STOP and RESTART instructions (PAUSE, RSTART) [BLm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                       |

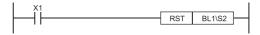

|                                 | Step START and END instructions (s, r) [Sn/BLm\Sn]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95                       |

|                                 | Forced transition EXECUTE & CANCEL instructions (s, r) [TRn/BLm\TRn]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

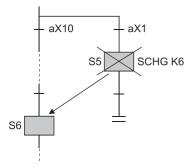

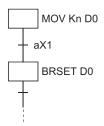

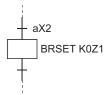

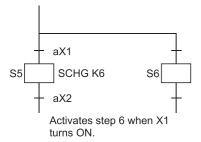

|                                 | Active step change instruction (SCHG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 101                      |

|                                 | Block switching instruction (BRSET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103                      |

| 4.5                             | SFC Information Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105                      |

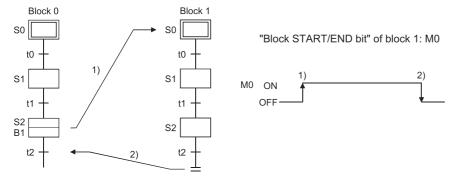

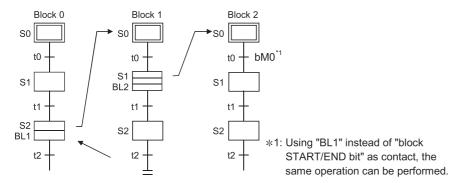

|                                 | Block START/END bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 106                      |

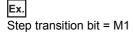

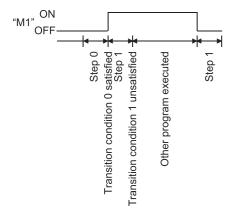

|                                 | Step transition bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 108                      |

|                                 | Block STOP/RESTART bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|                                 | Block STOP mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 112                      |

|                                 | Continuous transition bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 114                      |

|                                 | Number of active steps register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 116                      |

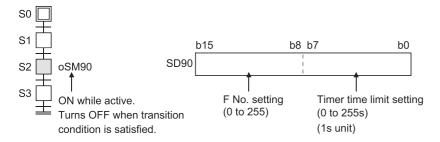

| 4.6                             | Step Transition Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

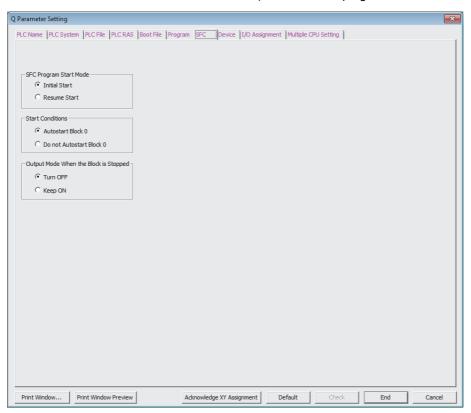

| 4.7                             | SFC Operation Mode Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

|                                 | SFC program start mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120                      |

|                                 | Block 0 START condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 122                      |

|                                 | Output mode at block STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 123                      |

|                                 | Periodic execution block setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 125                      |

|                                 | Operation mode at double block START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

|                                 | Operation mode at transition to active step (double step START)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

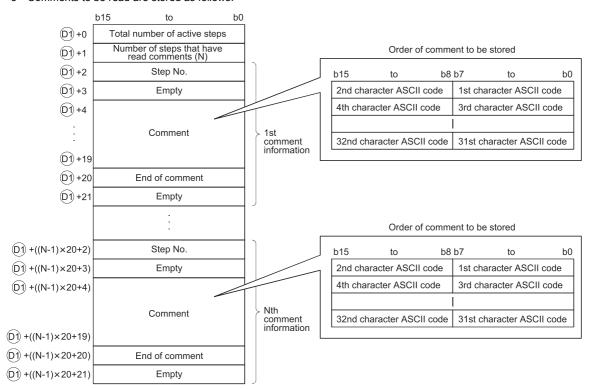

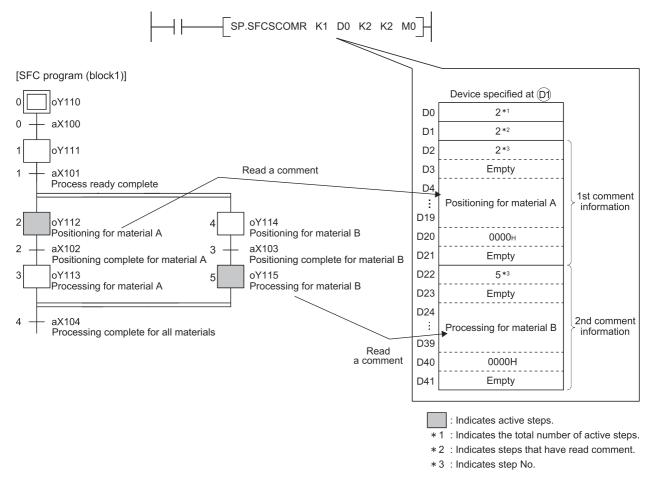

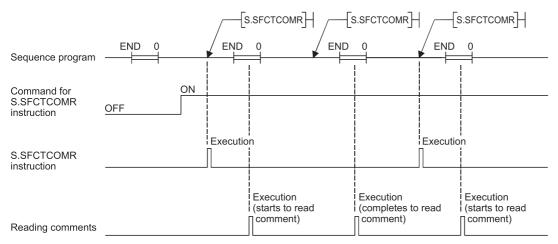

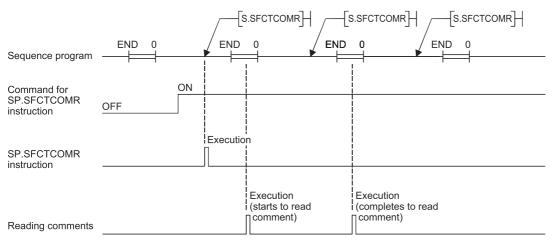

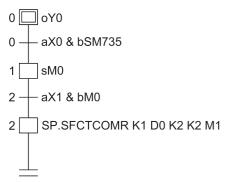

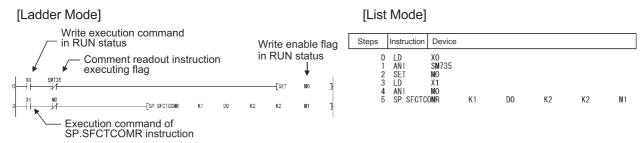

| 4.8                             | SFC Comment Readout Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

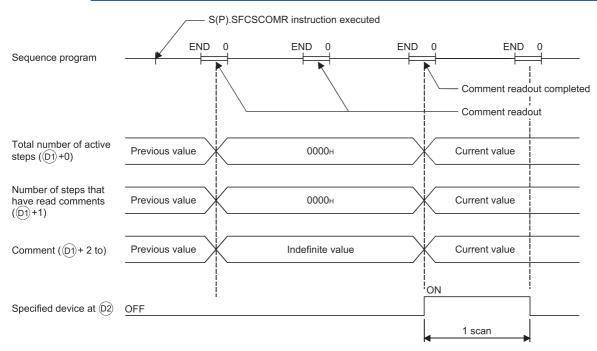

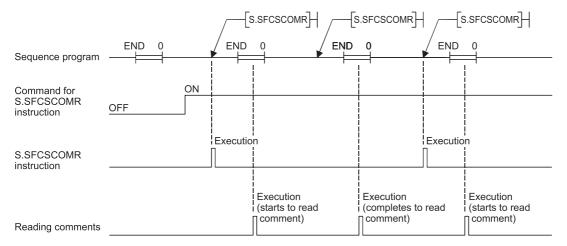

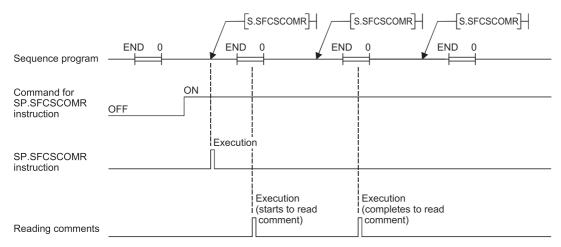

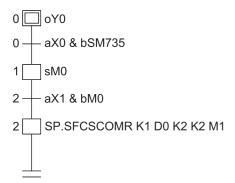

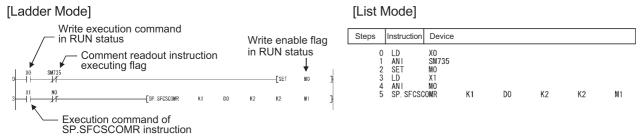

|                                 | SFC comment readout instruction (S(P). SFCSCOMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131                      |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

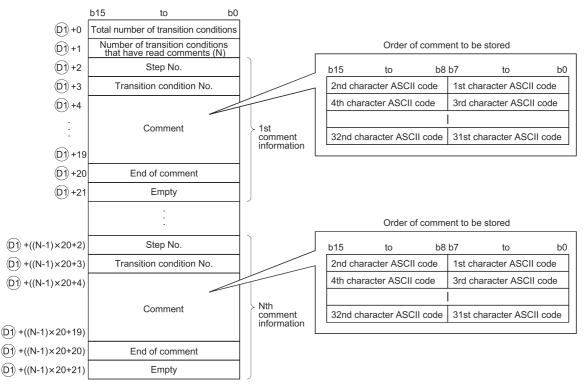

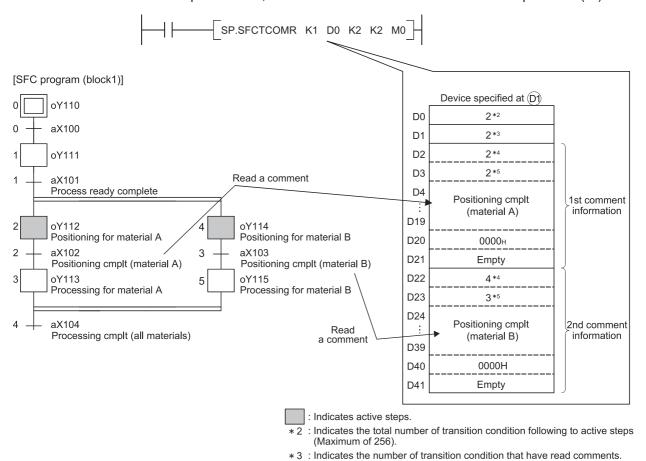

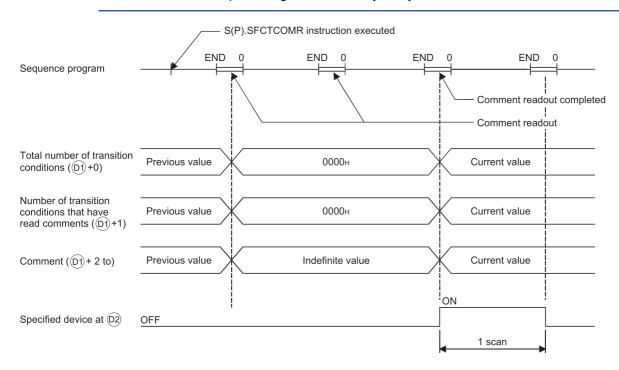

|                                 | SFC transition comment readout instruction (S(P). SFCTCOMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 138                      |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| CH#                             | SFC transition comment readout instruction (S(P). SFCTCOMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 138<br><b>145</b>        |

| CHA                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 145                      |

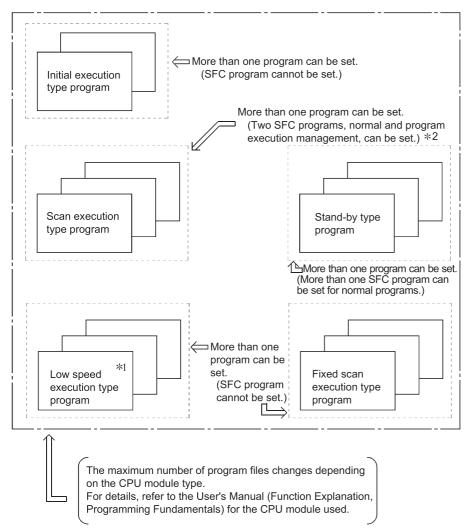

|                                 | APTER 5 SFC PROGRAM PROCESSING SEQUENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>145</b>               |

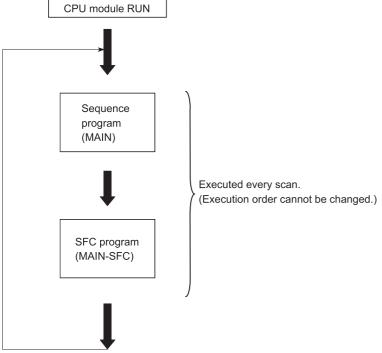

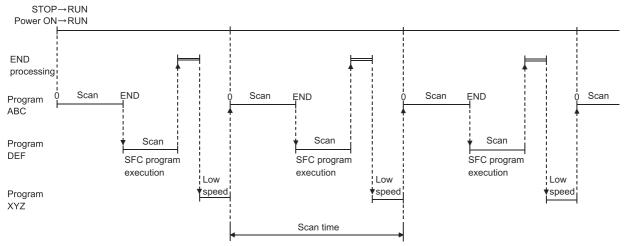

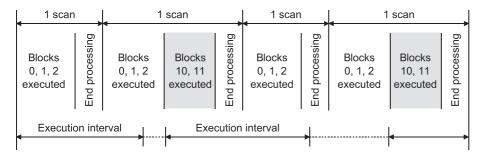

|                                 | APTER 5 SFC PROGRAM PROCESSING SEQUENCE  Whole Program Processing of Basic Model QCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>145</b> 145           |

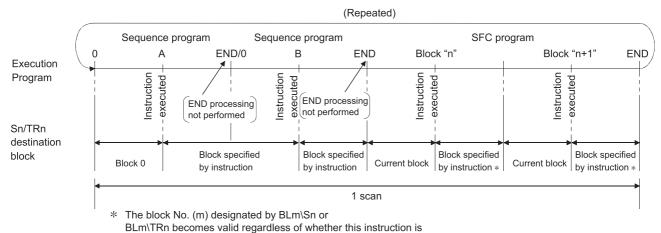

| 5.1                             | APTER 5 SFC PROGRAM PROCESSING SEQUENCE  Whole Program Processing of Basic Model QCPU  Whole program processing sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 145145 ant CPU,          |

| 5.1                             | Whole Program Processing of Basic Model QCPU  Whole program processing sequence  Whole Program Processing of High Performance Model QCPU, Process CPU, Redund                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 145145 ant CPU,146       |

| 5.1                             | Whole Program Processing of Basic Model QCPU  Whole program processing sequence.  Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU                                                                                                                                                                                                                                                                                                                                                                                                                          | 145                      |

| 5.1                             | Whole Program Processing of Basic Model QCPU  Whole program processing sequence  Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU  Whole program processing sequence                                                                                                                                                                                                                                                                                                                                                                                        | 145145145 ant CPU,146148 |

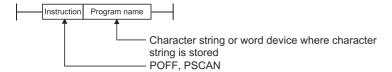

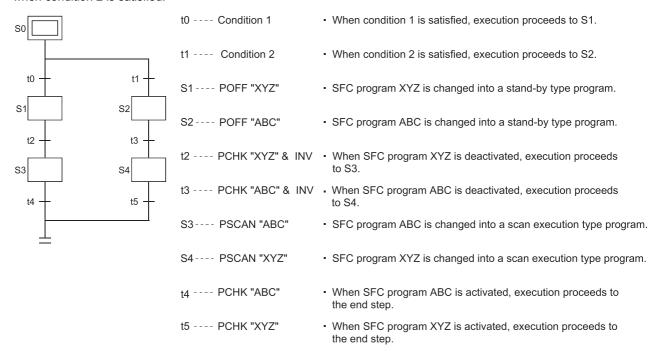

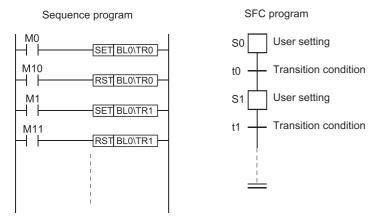

| 5.1                             | Whole Program Processing of Basic Model QCPU  Whole program processing sequence.  Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU  Whole program processing sequence.  Execution type designation by instructions                                                                                                                                                                                                                                                                                                                                          | 145                      |

| 5.1<br>5.2                      | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management                                                                                                                                                                                                                                                                                                   | 145                      |

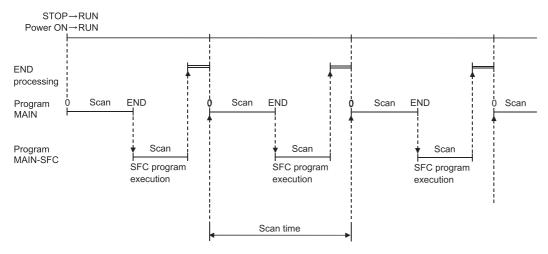

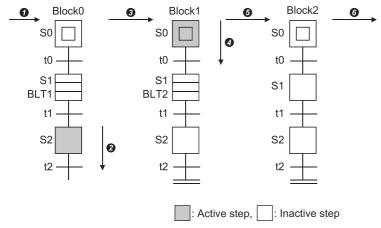

| 5.1<br>5.2                      | Whole Program Processing of Basic Model QCPU  Whole program processing sequence.  Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU  Whole program processing sequence.  Execution type designation by instructions  SFC program Processing Sequence.  SFC Program Processing Sequence.                                                                                                                                                                                                                                                                      | 145                      |

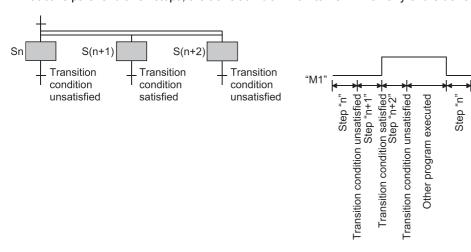

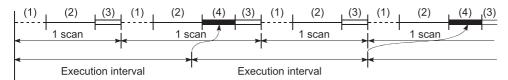

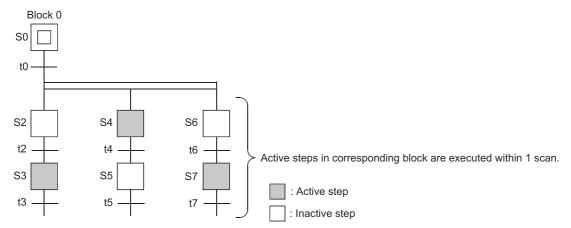

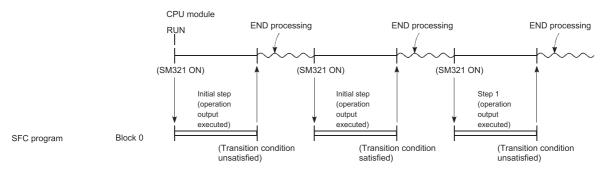

| 5.1<br>5.2                      | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management SFC Program Processing Sequence SFC program execution.                                                                                                                                                                                                                                            | 145                      |

| 5.1<br>5.2                      | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management SFC Program Processing Sequence SFC program execution. Block execution sequence.                                                                                                                                                                                                                  | 145                      |

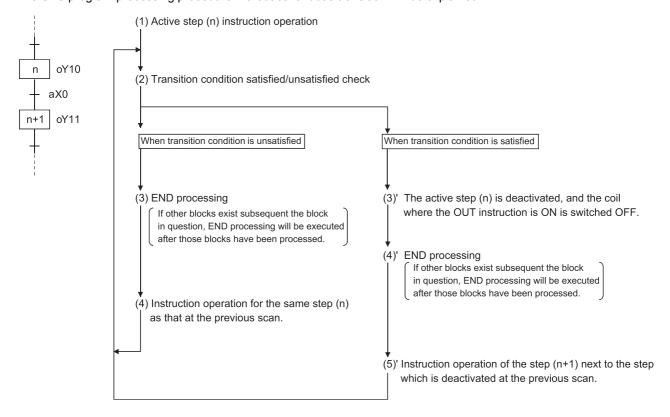

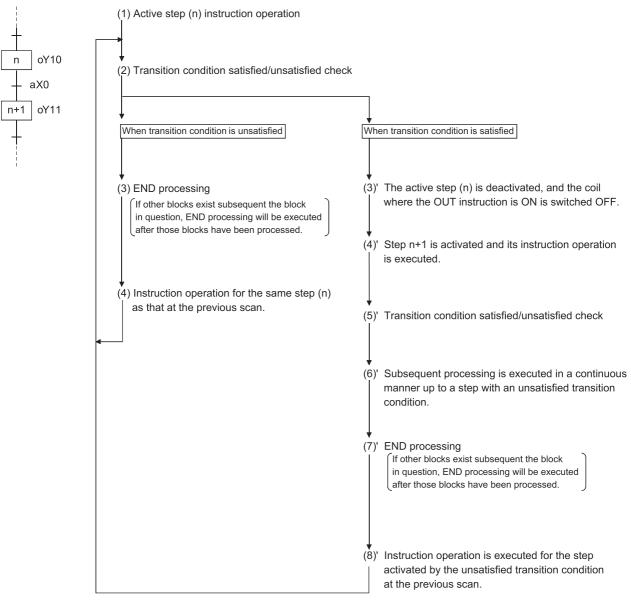

| 5.1<br>5.2                      | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management SFC Program Processing Sequence SFC program execution Block execution sequence Step execution sequence                                                                                                                                                                                            | 145                      |

| 5.1<br>5.2<br>5.3               | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management SFC Program Processing Sequence SFC program execution Block execution sequence Step execution sequence                                                                                                                                                                                            | 145                      |

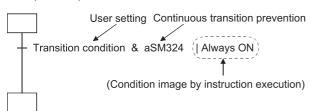

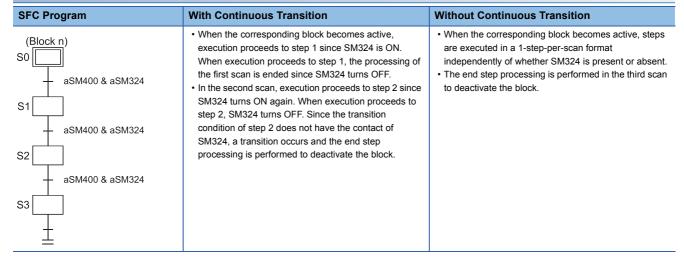

| 5.1<br>5.2<br>5.3               | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management SFC Program Processing Sequence SFC program execution. Block execution sequence. Step execution sequence Continuous transition ON/OFF operation                                                                                                                                                   | 145                      |

| 5.1<br>5.2<br>5.3               | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management SFC Program Processing Sequence SFC program execution. Block execution sequence Step execution sequence Continuous transition ON/OFF operation                                                                                                                                                    | 145                      |

| 5.1<br>5.2<br>5.3               | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management. SFC Program Processing Sequence SFC program execution. Block execution sequence Step execution sequence Continuous transition ON/OFF operation  APTER 6 SFC PROGRAM EXECUTION  SFC Program START and STOP.                                                                                       | 145                      |

| 5.1<br>5.2<br>5.3<br>CHA        | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence Execution type designation by instructions SFC program for program execution management. SFC Program Processing Sequence SFC program execution. Block execution sequence Step execution sequence Continuous transition ON/OFF operation  APTER 6 SFC PROGRAM EXECUTION  SFC Program resumptive START procedure.                                                                           | 145                      |

| 5.1<br>5.2<br>5.3<br>CHA        | Whole Program Processing of Basic Model QCPU Whole program processing sequence. Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence. Execution type designation by instructions SFC program for program execution management. SFC Program Processing Sequence. SFC program execution. Block execution sequence. Step execution sequence. Continuous transition ON/OFF operation  APTER 6 SFC PROGRAM EXECUTION  SFC Program START and STOP. SFC program resumptive START procedure. Block START and END                      | 145                      |

| 5.1<br>5.2<br>5.3<br>CHA<br>6.1 | Whole Program Processing of Basic Model QCPU Whole program processing sequence Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence. Execution type designation by instructions SFC program for program execution management. SFC Program Processing Sequence. SFC program execution. Block execution sequence. Step execution sequence. Continuous transition ON/OFF operation  APTER 6 SFC PROGRAM EXECUTION  SFC program resumptive START procedure. Block START and END Block START methods. Block END methods            | 145                      |

| 5.1<br>5.2<br>5.3<br>CHA        | Whole Program Processing of Basic Model QCPU Whole program processing sequence. Whole Program Processing of High Performance Model QCPU, Process CPU, Redund Universal Model QCPU, and LCPU Whole program processing sequence. Execution type designation by instructions SFC program for program execution management. SFC Program Processing Sequence. SFC program execution. Block execution sequence. Step execution sequence Continuous transition ON/OFF operation  APTER 6 SFC PROGRAM EXECUTION  SFC program start and STOP. SFC program resumptive START procedure. Block START and END. Block START methods. | 145                      |

|                    | Step START (Activate) and END (Deactivate) Methods                                                                                                                                                                           |       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                    | Step START (activate) methods                                                                                                                                                                                                |       |

|                    | Step END (deactivate) methods                                                                                                                                                                                                |       |

|                    | Changing an active step status (Not available for Basic model QCPU, Universal model                                                                                                                                          | QCPU, |

|                    | and LCPU)                                                                                                                                                                                                                    |       |

| 6.5                | Operation Methods for Continuous Transition                                                                                                                                                                                  | 16    |

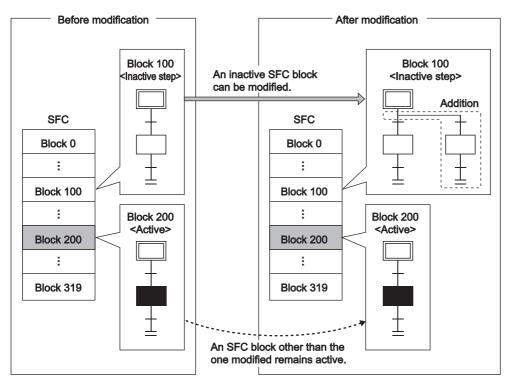

| 6.6                | Operation at Program Change                                                                                                                                                                                                  | 16    |

|                    | Operation at program change made by write to PLC                                                                                                                                                                             |       |

|                    | Program change by online change                                                                                                                                                                                              | 16    |

|                    | Online change (inactive block)                                                                                                                                                                                               | 16    |

| APF                | PENDICES                                                                                                                                                                                                                     | 174   |

| Арре               | endix 1 Special Relay and Special Register List                                                                                                                                                                              |       |

|                    | Special Relay (SM) List                                                                                                                                                                                                      | 17    |

|                    | Special Register (SD) List                                                                                                                                                                                                   | 17    |

| Арре               | endix 2 Restrictions on Basic Model QCPU, Universal Model QCPU, and LCPU                                                                                                                                                     |       |

|                    | and Alternative Methods                                                                                                                                                                                                      | 4.0   |

|                    | and Alternative Methods                                                                                                                                                                                                      |       |

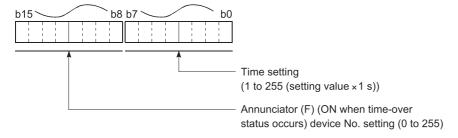

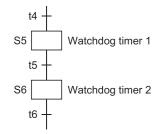

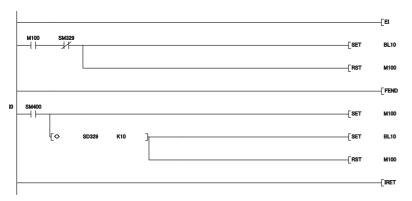

|                    | Step Transition Watchdog Timer Replacement Method                                                                                                                                                                            |       |

|                    |                                                                                                                                                                                                                              | 18    |

|                    | Step Transition Watchdog Timer Replacement Method                                                                                                                                                                            | 18    |

|                    | Step Transition Watchdog Timer Replacement Method                                                                                                                                                                            |       |

| IND                | Step Transition Watchdog Timer Replacement Method  Periodic Execution Block Replacement Method  Forced Transition Bit (TRn) Replacement Method  Active Step Change Instruction (SCHG) Replacement Method                     |       |

|                    | Step Transition Watchdog Timer Replacement Method  Periodic Execution Block Replacement Method  Forced Transition Bit (TRn) Replacement Method  Active Step Change Instruction (SCHG) Replacement Method  EX                 |       |

|                    | Step Transition Watchdog Timer Replacement Method  Periodic Execution Block Replacement Method  Forced Transition Bit (TRn) Replacement Method  Active Step Change Instruction (SCHG) Replacement Method                     |       |

| INS                | Step Transition Watchdog Timer Replacement Method  Periodic Execution Block Replacement Method  Forced Transition Bit (TRn) Replacement Method  Active Step Change Instruction (SCHG) Replacement Method  EX  TRUCTION INDEX |       |

| I <b>NS</b><br>REV | Step Transition Watchdog Timer Replacement Method  Periodic Execution Block Replacement Method  Forced Transition Bit (TRn) Replacement Method  Active Step Change Instruction (SCHG) Replacement Method  EX                 |       |

### **RELEVANT MANUALS**

| Manual name [manual number]                              | Description                                                            | Available form  |

|----------------------------------------------------------|------------------------------------------------------------------------|-----------------|

| GX Developer Version 8 Operating Manual (MELSAP-L)       | Describes how to create SFC programs using the software package for    | Print book      |

| [SH-080375E]                                             | creating SFC programs.                                                 | PDF             |

| GX Works2 Version1 Operating Manual (Common)             | Describes system configurations, parameter settings, online operations | Print book      |

| [SH-080779ENG]                                           | (common to Simple project and Structured project) of GX Works2.        | PDF             |

| QnUCPU User's Manual (Function Explanation, Program      | Describes the functions required for programming, programming          | Print book      |

| Fundamentals) [SH-080807ENG]                             | methods, and devices.                                                  | PDF             |

| Qn(H)/QnPH/QnPRHCPU User's Manual(Function Explanation,  | Describes the functions required for programming, programming          | Print book      |

| Program Fundamentals) [SH-080808ENG]                     | methods, and devices.                                                  | PDF             |

| MELSEC-L CPU Module User's Manual (Function Explanation, | Describes the functions required for programming, programming          | Print book      |

| Program Fundamentals) [SH-080889ENG]                     | methods, and devices.                                                  | e-Manual<br>PDF |

| MELSEC-Q/L Programming Manual (Common instruction)       | Describes how to use sequence instructions, basic instructions, and    | Print book      |

| [SH-080809ENG]                                           | application instructions.                                              | e-Manual<br>PDF |

e-Manual refers to the Mitsubishi Electric FA electronic book manuals that can be browsed using a dedicated tool.

e-Manual has the following features:

- Required information can be cross-searched in multiple manuals.

- Other manuals can be accessed from the links in the manual.

- The hardware specifications of each part can be found from the product figures.

- Pages that users often browse can be bookmarked.

### **TERMS**

Unless otherwise specified, this manual uses the following generic terms and abbreviations.

| Generic term                    | Description                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Basic                           | A generic term for the Q00JCPU, Q00CPU, and Q01CPU                                                                                                                                                                                                                                                |  |  |  |  |

| Basic model QCPU                |                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| High Performance                | A generic term for the Q02CPU, Q02HCPU, Q06HCPU, Q12HCPU, and Q25HCPU                                                                                                                                                                                                                             |  |  |  |  |

| High Performance model QCPU     |                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| High-speed Universal model QCPU | A generic term for the Q03UDVCPU, Q04UDVCPU, Q06UDVCPU, Q13UDVCPU, and Q26UDVCPU                                                                                                                                                                                                                  |  |  |  |  |

| LCPU                            | A generic term for the L02SCPU, L02SCPU-P, L02CPU, L02CPU-P, L06CPU, L06CPU-P, L26CPU-P, L26CPU-BT, and L26CPU-PBT                                                                                                                                                                                |  |  |  |  |

| Process CPU                     | A generic term for the Q02PHCPU, Q06PHCPU, Q12PHCPU, and Q25PHCPU                                                                                                                                                                                                                                 |  |  |  |  |

| Programming tool                | A generic term for GX Developer and GX Works2                                                                                                                                                                                                                                                     |  |  |  |  |

| QCPU                            | A generic term for the Basic model QCPU, High Performance model QCPU, Process CPU, Redundant CPU, and Universal model QCPU                                                                                                                                                                        |  |  |  |  |

| QnCPU                           | A generic term for the Q02CPU                                                                                                                                                                                                                                                                     |  |  |  |  |

| QnHCPU                          | A generic term for the Q02HCPU, Q06HCPU, Q12HCPU, and Q25HCPU                                                                                                                                                                                                                                     |  |  |  |  |

| QnPHCPU                         | A generic term for the Q02PHCPU, Q06PHCPU, Q12PHCPU, and Q25PHCPU                                                                                                                                                                                                                                 |  |  |  |  |

| QnPRHCPU                        | A generic term for the Q12PRHCPU and Q25PRHCPU                                                                                                                                                                                                                                                    |  |  |  |  |

| Redundant CPU                   | A generic term for the Q12PRHCPU and Q25PRHCPU                                                                                                                                                                                                                                                    |  |  |  |  |

| Universal                       | A generic term for the Q00UJCPU, Q00UCPU, Q01UCPU, Q02UCPU, Q03UDCPU, Q03UDVCPU, Q03UDECPU,                                                                                                                                                                                                       |  |  |  |  |

| Universal model QCPU            | Q04UDHCPU, Q04UDVCPU, Q04UDPVCPU, Q04UDEHCPU, Q06UDHCPU, Q06UDVCPU, Q06UDPVCPU, Q06UDPVCPU, Q06UDEHCPU, Q10UDEHCPU, Q13UDHCPU, Q13UDVCPU, Q13UDPVCPU, Q13UDEHCPU, Q20UDHCPU, Q26UDHCPU, Q26UDHCPU, Q26UDEHCPU, Q26UDEHCPU, Q30UDEHCPU, Q26UDEHCPU, Q26UDEHCPU, Q26UDEHCPU, Q26UDEHCPU, Q26UDEHCPU |  |  |  |  |

| Universal model Process CPU     | A generic term for the Q04UDPVCPU, Q06UDPVCPU, Q13UDPVCPU, and Q26UDPVCPU                                                                                                                                                                                                                         |  |  |  |  |

# 1 GENERAL DESCRIPTION

SFC, an abbreviation for "Sequential Function Chart", is a control specification description format in which a sequence of control operations is split into a series of steps to enable a clear expression of the program execution sequence and execution conditions.

This manual describes the specifications, functions, instructions, programming procedures, etc. used to perform programming with an SFC program using MELSAP-L.

MELSAP-L can be used with the following CPU modules.

MELSAP-L conforms to the IEC Standard for SFC.

- Basic model QCPU whose serial number (first five digits) is 04122 or later

- · High Performance model QCPU

- · Process CPU

- · Redundant CPU

- · Universal model QCPU

- LCPU

In this manual, MELSAP-L is referred to as SFC (program, diagram).

- The following functions cannot be executed if a parameter that sets the "high speed interrupt cyclic interval" is loaded into a High Performance model QCPU of which the first 5 digits of the serial number are "04012" or later.

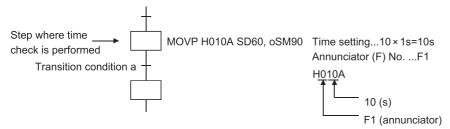

- Page 117 Step Transition Watchdog Timer

- Page 119 SFC Operation Mode Setting

- The QCPU-A (A mode) cannot use MELSAP-L explained in this manual.

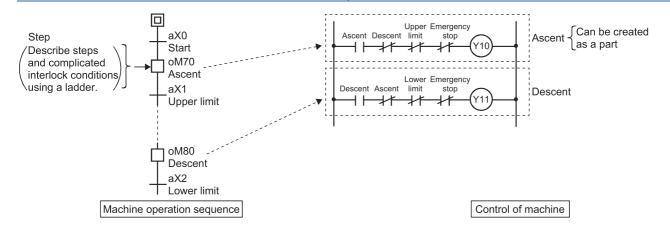

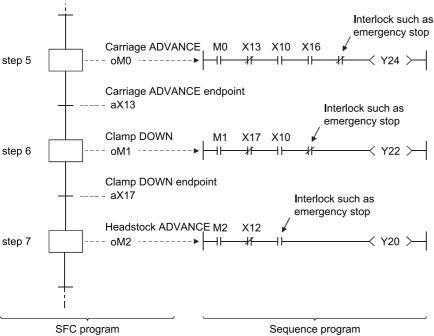

#### When created with MELSAP-L and ladders

#### **MELSAP-L** side

#### Sequence programs side

The flow of operation is easy to understand by creating the SFC program related to the interlock conditions.

The area can be developed into a product by creating interlock conditions irrelevant to the flow of operation.

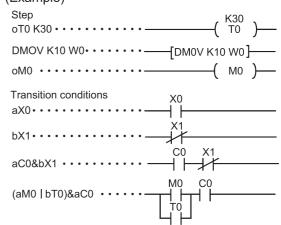

### **Description format with MELSAP-L**

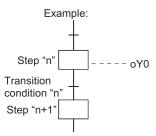

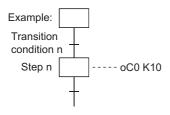

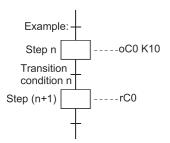

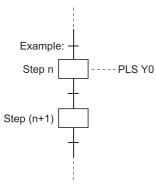

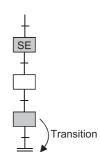

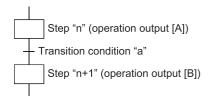

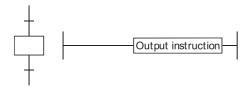

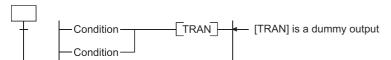

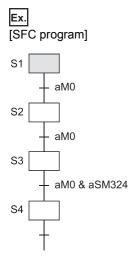

The description format in the step and transition conditions with MELSAP-L is shown b. (Example)

Commands equivalent to contacts cannot be described in the step.

### 1.1 Description of SFC Program

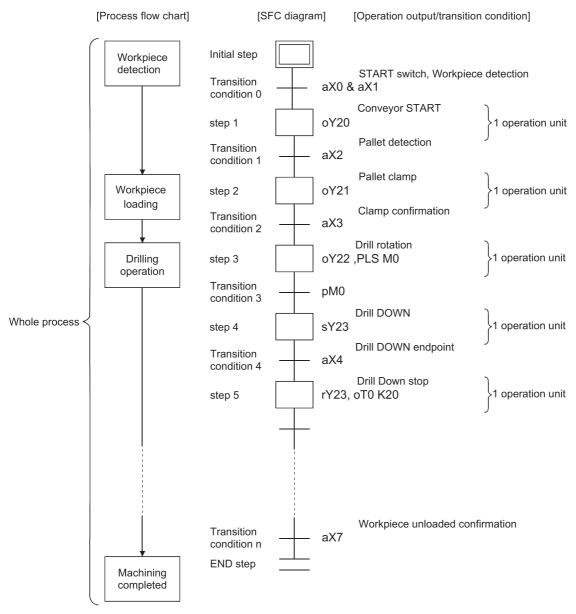

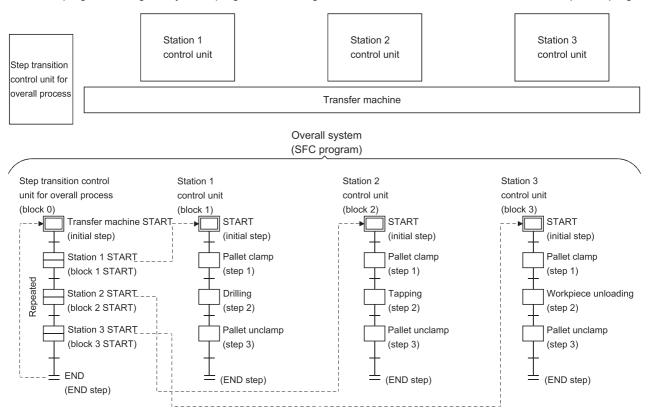

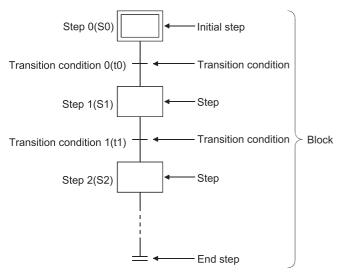

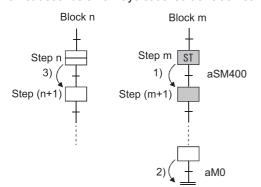

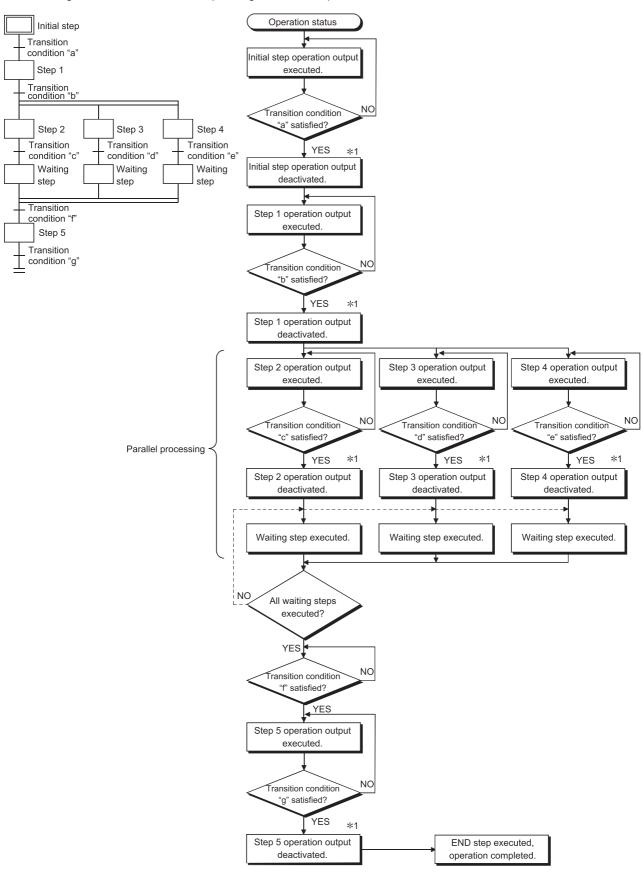

The SFC program consists of steps that represent units of operations in a series of machine operations.

In each step, the actual detailed control is programmed by using a ladder circuit.

Grouping steps into one block in process units allows to create an SFC program that is capable of tracking all the processes as well as structuring the operation flow in each process.

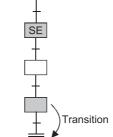

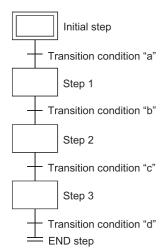

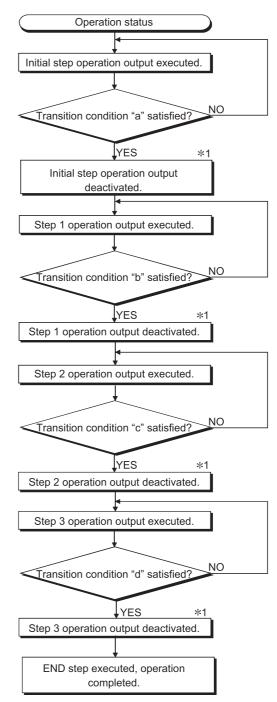

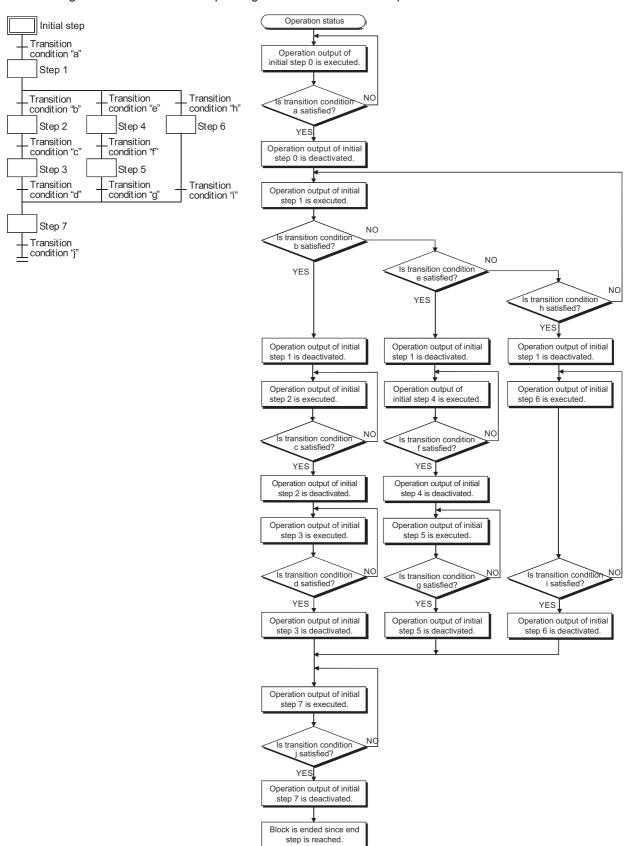

An SFC program starts at an initial step, executes a step following a transition condition in due order every time that transition condition is satisfied, and ends a series of operations at an end step.

- · When the SFC program is started, the "initial" step is executed first.

- Execution of the initial step continues until transition condition 0 is satisfied. When this transition condition is satisfied, execution of the initial step is stopped, and processing proceeds to the step which follows the initial step.

Processing of the SFC program continues from step to step in this manner until the END step has been executed.

### 1.2 SFC (MELSAP-L) Features

This section describes the SFC (MELSAP-L) features.

### Easy to design and maintain systems

It is possible to correspond the controls of the entire facility, mechanical devices of each station, and all machines to the blocks and steps of the SFC program on a one-to-one basis. Because of this capability, systems can be designed and maintained with ease even by those with relatively little knowledge of sequence programs.

Moreover, programs designed by other programmers using this format are much easier to decode than sequence programs.

### Program development efficiency is enhanced by dividing control into parts

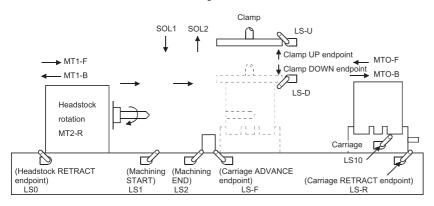

The machine control process can be divided into parts by describing the operation sequence and machine control separately. The MELSAP-L is used to describe the operation sequence for the machine, and a sequence program (circuit/list) is used to describe the machine control including individual interlock.

### Block and step configurations can easily be changed for new control applications

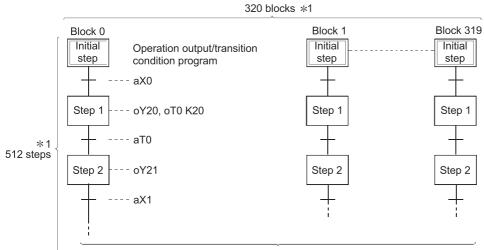

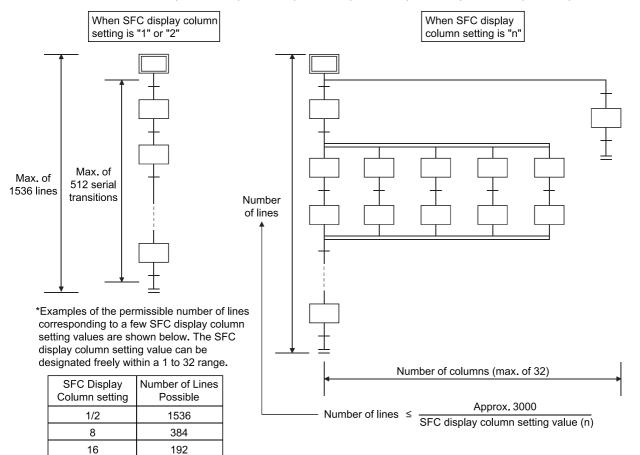

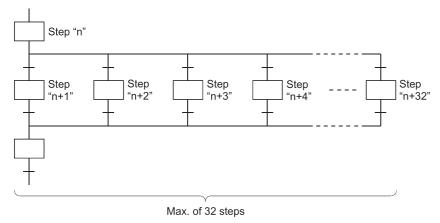

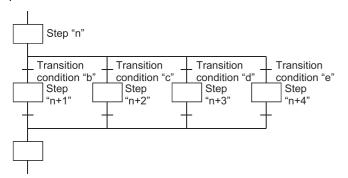

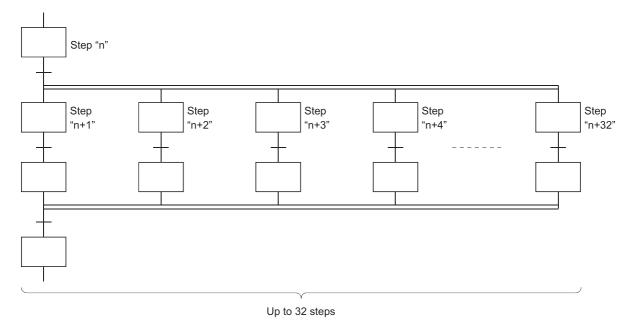

- A total of 320 blocks<sup>\*1</sup> can be created in an SFC program.

- Up to 512 steps\*1 can be created per block.

- Up to 2K sequence steps of operation outputs/transition conditions can be created in all blocks.

Reduced tact times, as well as easier debugging and trial run operations are possible by dividing blocks and steps as follows:

- · Divide blocks properly according to the operation units of machines.

- · Divide steps in each block properly.

Operation output/transition condition: 2k sequence steps in all blocks

- \*1 For the following CPU modules, 128 blocks and 128 steps can be created.

- · Basic model QCPU

- · Universal model QCPU (Q00UJCPU, Q00UCPU, Q01UCPU, Q02UCPU)

- · LCPU (L02SCPU, L02SCPU-P, L02CPU, L02CPU-P)

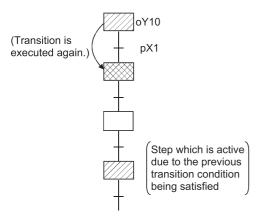

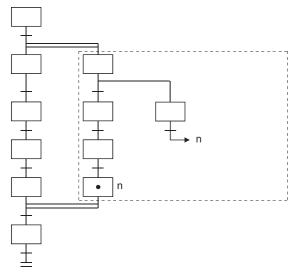

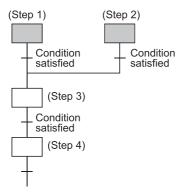

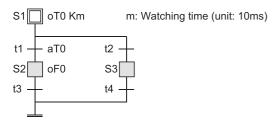

### Creation of multiple initial steps is possible

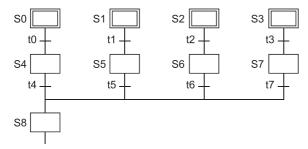

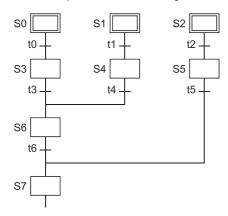

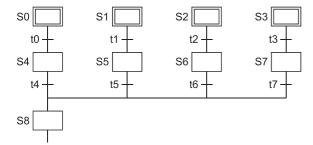

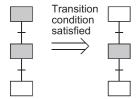

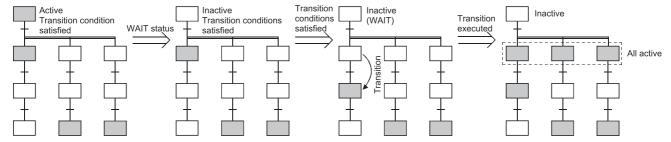

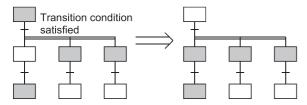

Multiple processes can easily be executed and combined. Initial steps are linked using a "selection coupling" format. When multiple initial steps (S0 to S3) are active, the step where the transition condition (t4 to t7) immediately prior to the selected coupling is satisfied becomes inactive, and a transition to the next step occurs.

Moreover, when the transition condition immediately prior to an active step is satisfied, the next step is executed in accordance with the parameter settings.

Basic model QCPU, Universal model QCPU, and LCPU cannot be selected in the parameter setting. It operates in the default "Transfer" mode.

- Wait: Transition to the next step occurs after waiting for the next step to become inactive.

- Transfer: Transition to the next step occurs even if the next step is active. (Default)

- Pause: An error occurs if the next step is active.

Linked steps can also be changed at each initial step.

### Program design is easy due to a wealth of step attributes

A variety of step attributes can be assigned to each step. Used singly for a given control operation, or in combination, these attributes greatly simplify program design procedures.

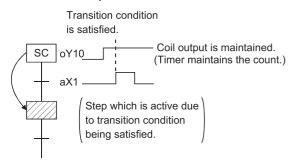

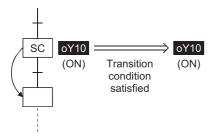

#### **■**Types of HOLD steps, and their operations

· Coil HOLD step

- After transition, the operation of the operation output is continued (put in HOLD status) and the coil output status when the transition condition is satisfied is maintained.

- Transition will not occur if the transition condition is satisfied again.

- Convenient for maintaining an output until the corresponding block is completed (hydraulic motor output, pass confirmation signal, etc.).

- When the output mode at block stop is OFF, it remains OFF after a block restart

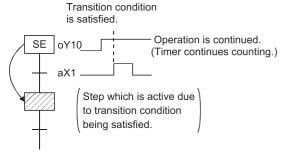

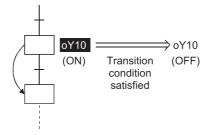

- Operation HOLD step (no transition check)

- After transition, the operation of the operation output is continued (put in HOLD status).

- · Transition will not occur if the transition condition is satisfied again.

- When the output mode at block stop is OFF, the operation is continued after a block restart, and therefore, the output is provided as a result of the operation that has been performed.

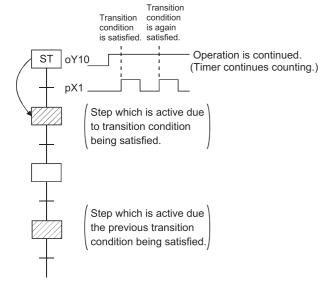

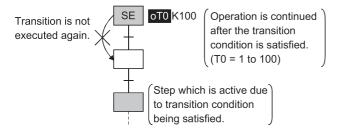

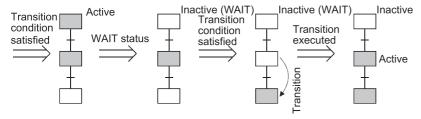

· Operation HOLD step (with transition check)

- After transition, the operation of the operation output is continued (put in HOLD status)

- When the transition condition is satisfied again, transition is executed and the next step is reactivated.

- Operation output processing is executed at the reactivated next step. When the transition condition is satisfied, transition occurs, and the step is deactivated.

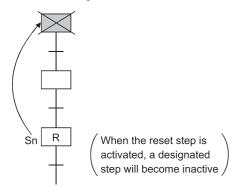

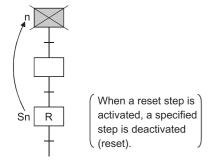

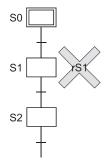

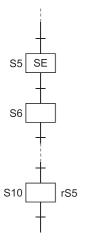

### **■**Reset step

When a HOLD status becomes unnecessary for machine control, or on selective branching to a manual ladder occurs after an error detection, etc., a reset request can be designated for the HOLD step, deactivating the step in question.

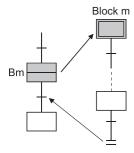

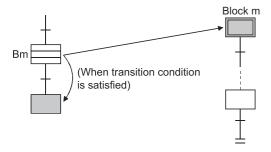

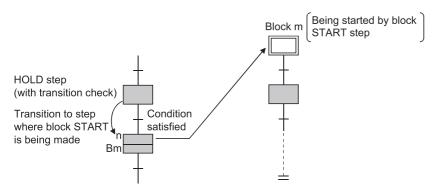

### ■Types of block START steps, and their operations

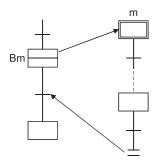

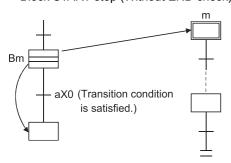

• Block START step (with END check)

• Block START step (Without END check)

- In the same manner as for a subroutine CALL-RET, a START source block transition will not occur until the end of the START destination block is reached.

- Convenient for starting the same block several times, or to use several blocks together, etc.

- A convenient way to return to the START source block and proceed to the next process block when a given process is completed in a processing line, for example.

- Even if the START destination block is active, a START source block transition

occurs when the transition condition associated with the block START step is

satisfied. At this time, the processing of the START destination block will be

continued unchanged until the end step is reached.

- By starting another block at a given step, the START destination block can be controlled independently and asynchronously with the START source block until processing of the current block is completed.

### A given function can be controlled in a variety of ways according to the application

Block functions such as START, END, temporary stop, restart, and forced activation and ending of specified steps can be controlled by SFC diagram symbols, SFC control instructions, or by SFC information registers.

| Control method                     | Description                                                                                                                                               |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control by SFC diagram symbols     | Convenient for control of automatic operations with easy sequential control.                                                                              |

| Control by SFC instructions        | Enables requests from program files other than the SFC, and is convenient for error processing, for example after emergency stops, and interrupt control. |

| Control by SFC information devices | Enables control of SFC peripheral devices, and is convenient for partial operations such as debugging or trial runs.                                      |

Functions which can be controlled by multiple methods are shown below.

| Function                       | Control Method |                          |                             |  |  |  |

|--------------------------------|----------------|--------------------------|-----------------------------|--|--|--|

|                                | SFC Diagram    | SFC Control Instructions | SFC Information Registers   |  |  |  |

| Block START (with END wait)    | Bm 📙           | _                        | _                           |  |  |  |

| Block START (without END wait) | Bm 🗐           | sBLm                     | Block START/END bit ON      |  |  |  |

| Block END                      | <u></u>        | rBLm                     | Block START/END bit OFF     |  |  |  |

| Block STOP                     | _              | PAUSE BLm                | Block PAUSE/RESTART bit ON  |  |  |  |

| Restart stopped block          | _              | RSTART BLm               | Block PAUSE/RESTART bit OFF |  |  |  |

| Forced step activation         | _              | • sSn<br>• sBLm\Sn       | _                           |  |  |  |

| Forced step END                | Sn R           | • rSn<br>• rBLm\Sn       | _                           |  |  |  |

In cases where the same function can be executed by a number of methods, the first control method which has been designated by the request output to the block or step in question will be the effective control method. Functions controlled by a given control method can be canceled by another control method.

For block START, the active block started by the SFC diagram can be forcibly ended by executing the SFC control instruction before the END step or by turning OFF the block START/END bit of the SFC information devices.

### Automatic scrolling function enables quick identification of machine system troubles

The execution of an active (execution) block, an active (execution) step, an operation output/transition condition can be monitored (with the automatic scrolling function) from peripheral devices. Moreover, the transition watchdog function enables the detection of the step where transition does not occur after the designated time elapses. These monitoring functions allow you to track down the spot where a problem occurs without a broad knowledge about sequence programs.

# 2 SYSTEM CONFIGURATION

This chapter describes the system configuration of the SFC program.

### 2.1 Applicable CPU Modules

MELSAP-L (SFC programs) runs on the following CPU modules.

| CPU module type             | Model name                                                                                                                                                                                                                                                                                                               |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic model QCPU*1          | Q00JCPU, Q00CPU, Q01CPU                                                                                                                                                                                                                                                                                                  |

| High Performance model QCPU | Q02CPU, Q02HCPU, Q06HCPU, Q12HCPU, Q25HCPU                                                                                                                                                                                                                                                                               |

| Process CPU                 | Q02PHCPU, Q06PHCPU, Q12PHCPU, Q25PHCPU                                                                                                                                                                                                                                                                                   |

| Redundant CPU               | Q12PRHCPU, Q25PRHCPU                                                                                                                                                                                                                                                                                                     |

| Universal model QCPU        | Q00UJCPU, Q00UCPU, Q01UCPU, Q02UCPU, Q03UDCPU, Q03UDVCPU, Q03UDECPU, Q04UDHCPU, Q04UDEHCPU, Q04UDPVCPU, Q06UDPVCPU, Q06UDVCPU, Q06UDPVCPU, Q06UDEHCPU, Q10UDHCPU, Q10UDEHCPU, Q13UDHCPU, Q13UDVCPU, Q13UDPVCPU, Q13UDEHCPU, Q20UDHCPU, Q20UDEHCPU, Q26UDPVCPU, Q26UDEHCPU, Q26UDHCPU, Q26UDPVCPU, Q26UDEHCPU, Q20UDEHCPU |

| LCPU                        | L02SCPU, L02SCPU-P, L02CPU, L02CPU-P, L06CPU, L06CPU-P, L26CPU, L26CPU-P, L26CPU-BT, L26CPU-PBT                                                                                                                                                                                                                          |

<sup>\*1</sup> Modules whose serial number (first five digits) is 04122 or later

### 2.2 Peripheral Devices for SFC Programs

The following peripheral devices can be used to create, edit and monitor SFC programs. The numbers in the following table mean (1): Basic model QCPU, (2): High Performance model QCPU, (3): Process CPU, (4): Redundant CPU, (5): Universal model QCPU, and (6): LCPU.

O: Available, ×: Not available, △: Partly available

| Peripheral device | Software package to be installed in a personal computer |   | CPU module |     |     |     |     |  |

|-------------------|---------------------------------------------------------|---|------------|-----|-----|-----|-----|--|

|                   |                                                         |   | (2)        | (3) | (4) | (5) | (6) |  |

| Personal computer | SW4D5C-GPPW-E or later                                  | × | 0          | ×   | ×   | ×   | ×   |  |

| (Windows®         | GX Developer Version 7.10L (SW7D5C-GPPW-E) or later     | × | 0          | △*2 | ×   | ×   | ×   |  |

| compatible)       | GX Developer Version 8 (SW8D5C-GPPW-E) or later         | 0 | 0          | △*2 | ×   | ×   | ×   |  |

|                   | GX Developer Version 8.18U (SW8D5C-GPPW-E) or later     | 0 | 0          | △*2 | 0   | ×   | ×   |  |

|                   | GX Developer Version 8.48A (SW8D5C-GPPW-E) or later     | 0 | 0          | △*2 | 0   | △*1 | ×   |  |

|                   | GX Developer Version 8.62Q (SW8D5C-GPPW-E) or later     | 0 | 0          | △*2 | 0   | △*3 | ×   |  |

|                   | GX Developer Version 8.68W (SW8D5C-GPPW-E) or later     | 0 | 0          | 0   | 0   | △*4 | ×   |  |

|                   | GX Developer Version 8.78G (SW8D5C-GPPW-E) or later     | 0 | 0          | 0   | 0   | △*5 | ×   |  |

|                   | GX Developer Version 8.89T (SW8D5C-GPPW-E) or later     | 0 | 0          | 0   | 0   | △*5 | △*9 |  |

|                   | GX Works2 Version 1.24A (SW1DNC-GXW2-E) or later        | × | 0          | ×   | ×   | △*5 | △*9 |  |

|                   | GX Works2 Version 1.25B (SW1DNC-GXW2-E) or later        | × | 0          | ×   | ×   | △*6 | △*9 |  |

|                   | GX Works2 Version 1.56J (SW1DNC-GXW2-E) or later        | × | 0          | ×   | ×   | △*6 | △*7 |  |

|                   | GX Works2 Version 1.98C (SW1DNC-GXW2-E) or later        | 0 | 0          | 0   | 0   | 0   | △*8 |  |

|                   | GX Works2 Version 1.492N (SW1DNC-GXW2-E) or later       | 0 | 0          | 0   | 0   | 0   | 0   |  |

- \*1 Available only with the Q02UCPU, Q03UDCPU, Q04UDHCPU, and Q06UDHCPU

- \*2 Available only with the Q12PHCPU and Q25PHCPU

- \*3 Available only with the Q02UCPU, Q03UDCPU, Q04UDHCPU, Q06UDHCPU, Q13UDHCPU, and Q26UDHCPU

- \*4 Available only with the Q02UCPU, Q03UD(E)CPU, Q04UD(E)HCPU, Q06UD(E)HCPU, Q13UD(E)HCPU, and Q26UD(E)HCPU

- \*5 Available only with the Q00U(J)CPU, Q01UCPU, Q02UCPU, Q03UD(E)CPU, Q04UD(E)HCPU, Q06UD(E)HCPU, Q10UD(E)HCPU, Q13UD(E)HCPU, Q20UD(E)HCPU and Q26UD(E)HCPU

- \*6 Available only with the Q00UJCPU, Q00UCPU, Q01UCPU, Q02UCPU, Q03UDCPU, Q03UDECPU, Q04UDHCPU, Q04UDHCPU, Q04UDHCPU, Q10UDHCPU, Q10UDHCPU, Q13UDHCPU, Q13UDHCPU, Q20UDHCPU, Q20UDHCPU, Q20UDHCPU, Q20UDHCPU, Q20UDHCPU, Q10UDHCPU, Q20UDHCPU, Q20UDHCPU, Q20UDHCPU, Q50UDHCPU, Q50

- \*7 Available only with the L02CPU, L02CPU-P, L26CPU-BT, and L26CPU-PBT

- \*8 Available only with the L02SCPU, L02CPU, L02CPU-P, L26CPU, L26CPU-BT, and L26CPU-PBT

- \*9 Available only with the L02CPU and L26CPU-BT

# 3 SPECIFICATIONS

This chapter describes the specifications of SFC programs.

# 3.1 Performance Specifications Related to SFC Programs

This section describes the performance specifications of SFC programs.

#### **Basic model QCPU**

#### **■**Performance specifications

| Item                                    |                                                            | Q00JCPU                                                            | Q00CPU        | Q01CPU         |  |  |  |

|-----------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------|---------------|----------------|--|--|--|

| SFC program                             | Capacity                                                   | Max. 8k steps                                                      | Max. 8k steps | Max. 14k steps |  |  |  |