# **BOID'S POUR Systems**® 4in1 400A/1200V Module with T-type Topology for 3-Level Applications

A growing demand for 3-level inverter technology combining reduced power loss and increased power capacity is originating from power conversion applications like wind and PV inverter as well as from industrial equipment such as uninterruptible power supplies (UPS) and recently active frontends of 4-quadrant drives.

# By Marco Honsberg and Thomas Radke, Mitsubishi Electric Europe B.V.

Much attention has focused on the further development of power semiconductor modules being the key devices in inverters, that offer low power consumption, reduced package size and especially low inductance to help maximizing the 3-level inverter's performance.

Figure 1: Photo of CM400ST-24S1

Mitsubishi Electric launched the CM400ST-24S1 IGBT, e.g. a 4in1 400A/1200V IGBT module as part of a new family of power semiconductor modules optimized for 3-level inverters to meet these demands by adopting new packages that help reducing inductance, thereby contributing to reduced power consumption and downsizing in largecapacity industrial equipment.

## Module ratings

This new 400A/1200V module represents the biggest current rating of a planned lineup of 4in1 3-level IGBT modules planned in the same package. Based on electrical and thermal evaluations the CM400ST-24S1 is supposed to operate in 125kW-class inverters.

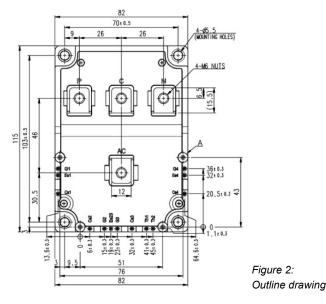

The photo of the CM400ST-24S1 reveals the outline of the package and figure 2 indicates the drawing of this new package. With baseplate dimensions of 115mm x 82mm and the innovative step terminal design this new outline provides new degrees of freedom in designing a power stage including the mechanical design of a gate driver Printed Circuit Board and an efficient utilization of the heatsink in case of parallel connection of modules. The next paragraph will introduce the design features that have led to such an innovative IGBT module packaging concept.

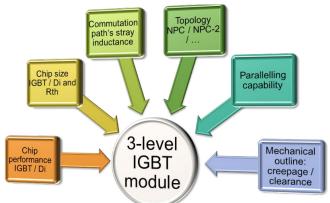

Figure 3: Design considerations for 3-level modules

February 2015

#### Design considerations for the CM400ST-24S1

Figure 3 shows at a glance the design considerations that have significantly influenced the concept of this new IGBT module CM400ST-24S1. In fact a state-of-the-art 3-level IGBT module shall reflect a best adoption of design aspects as shown in figure 3 to deliver the desired performance.

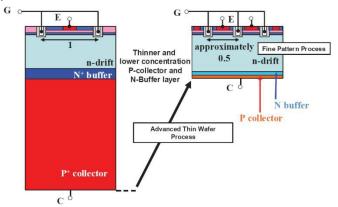

Figure 4: 7<sup>th</sup> generation chip technology

#### Chip performance IGBT / Di

Obviously the chip performance itself of the IGBTs and Diodes play one major role in the design of a 3-level IGBT module. In case of the CM400ST-24S1 the latest chip generation of Carrier Stored Trench gate Bipolar Transistors (CSTBT<sup>™</sup>) have been adopted. Thus, for 1200V blocking voltage class a 6.1<sup>st</sup> generation CSTBT<sup>™</sup> chip has been selected offering today's best trade-off between switching and conduction loss in this voltage class along with 650V CSTBT<sup>™</sup> chip of the 7<sup>th</sup> generation chip technology for the first time introduced in an industrial grade IGBT module. Figure 4 shows the innovative 7<sup>th</sup> generation chip technology which has improved trade-off between static loss Vce(sat) and dynamic loss as specific turn off energy E(off).

In this 7<sub>th</sub> generation 650V chip substantial modifications of the fabrication technology have led to a significant performance improvement. The manufacturing techniques applied to this novel 650V CSTBT<sup>M</sup> allowed an about half-size shrinkage of the transistor unit cell through a fine pattern process and a LPT (Light Punch Through) structure utilizing an advanced thin wafer process technology.

#### Topology

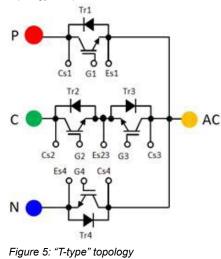

For DC-link voltage ranges up to about 850V a so called "T-type" topology has proven to be the best choice considering the switch-

ing frequency range of the application. The CM400ST-24S1 is made for DC-link voltages of up to 850V and is following this topology indicated in figure 5 utilizing the aforementioned 6.1st generation C<sup>ST</sup>BT™ 1200V class IGBT and anti-paralleled diodes for Tr1 and Tr4 and the novel 650V 7th generation CSTBT™ chips with anti-paralleled diode for Tr2 and Tr3.

#### Stray inductance

The module's internal stray inductance in conjunction with the blocking voltage capability of the chosen chips their dynamic loss performance and the desired performance of the module are key optimization objectives. Referring to the complexity of potential current and commutation paths of a T-type 3-level IGBT module, e.g. at least from terminal "P" to terminal "C" and from terminal "C" to "N" in a typical 3L commutation loop the module design must minimize the inductance for at least those two commutation paths. The CM400ST-24S1 has reached for both mentioned 3-level commutation loops stray inductance levels of less than 30nH (approximately 26nH) and additionally a commutation stray inductance of about 30nH in the 2-level commutation path from terminal "P" to terminal "N". The balanced low stray inductance layout of this new package incorporates a new degree of freedom to alter from 3-level commutation strategy to a 2-level commutation operation providing a better thermal exploitation of the semiconductor chips at high current and low modulation indices to cover for example extraordinary operating conditions of uninterruptible Power Supplies (UPS).

#### Chip size and thermal resistance (Rth)

The CM400ST-24S1 employs Silicon – Nitride substrate (Si3N4) to provide the required thermal performance of the package. This material's thermal conductivity is in between the superior performance of the Aluminum Nitride (ALN) and the worse performing Aluminum oxide (Al2O3). Referring to the topology as shown in figure 5 the thermal performance of each chip could be optimized for certain applications. Hence, an anti-paralleled Di to Tr1 or Tr4 could be sized comparatively small for a motor drive application operating at high power factor but they should be sized much bigger for a module placed in an active frontend mainly operating in Power factor Correction (PFC) mode. Indeed the CM400ST-24S1 chip size ratio has been selected to satisfy both applications.

#### Paralleling capability

Paralleling capability is an essential feature of the CM400ST-24S1, since it permits utilizing the same module for a modular design for output power requirements of more than the mentioned 125kW. Providing paralleling as dedicated feature implies constructing the module in order to minimize the distance between DC-link terminals of the paralleled modules and to provide a (simple) layout that utilizes the heatsink area and blower construction efficiently. The module dimensions of 82mm x 115mm, whereas the shorter 82mm is the dimension that advantageously decreases the distance between two adjacent modules efficiently. The step terminal approach for the output terminal simplifies the connection to parallel modules while this different height level will refrain from disturbing the DC-link construction of terminals "P", "C" and "N".

The CM400ST-24S1 has been designed to provide a high performing low inductive IGBT module solution for 3-level applications with a maximum DC-link voltage of 850V. The innovative package construction realizes low inductance in all possible commutation loops and by the step terminal it is dedicated for paralleling application for active frontend (PFC) as well as for PV and UPS output application. The low thermal resistance along with the loss performance of the latest generation of utilized IGBT and diode chips provides unprecedented output power performance of a 3-level IGBT module in this configuration. The first module that is available is a 400A class current rated module. A further lineup of smaller current ratings is planned.

marco.honsberg@meg.mee.com

thomas.radke2@meg.mee.com

### www.mitsubishichips.eu