<DIPIPM>

# Super mini DIPIPM Ver.7 Series APPLICATION NOTE PSSxxS93x6-AG

### **Table of contents**

| CHAPTER 1 INTRODUCTION                                                                                                         |                      |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1 Features of Super mini DIPIPM Ver.7                                                                                        | 2                    |

| 1.2 Functions                                                                                                                  |                      |

| 1.3 Target Applications                                                                                                        |                      |

| 1.4 Product Line-up                                                                                                            | 4                    |

| 1.5 The Difference's between Previous Series and This Series (PSS**S93*6-AG)                                                   |                      |

| CHAPTER 2 SPECIFICATIONS AND CHARACTERISTICS                                                                                   |                      |

| 2.1 Super Mini DIPIPM Ver.7 Specifications                                                                                     | 7                    |

| 2.1.1 Maximum Ratings                                                                                                          | 7                    |

| 2.1.2 Thermal Resistance                                                                                                       |                      |

| 2.1.4 Mechanical Characteristics and Ratings                                                                                   | 13                   |

| 2.2 Protective Functions and Operating Sequence                                                                                | 14                   |

| 2.2.1 Short Circuit Protection                                                                                                 |                      |

| 2.2.3 OT Protection (PSS**S93E6-AG only)                                                                                       | 18                   |

| 2.2.4 Temperature output function Vot (PSS**S93F6-* only)                                                                      |                      |

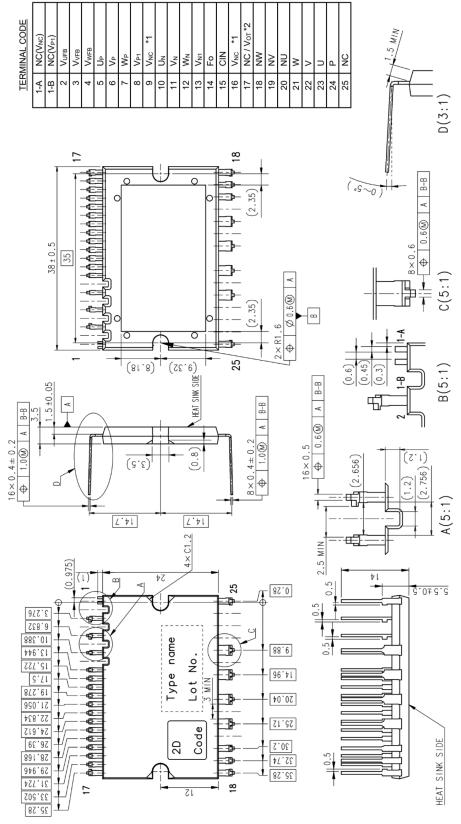

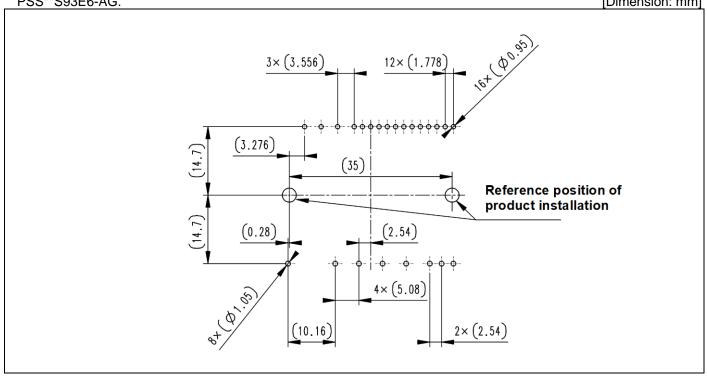

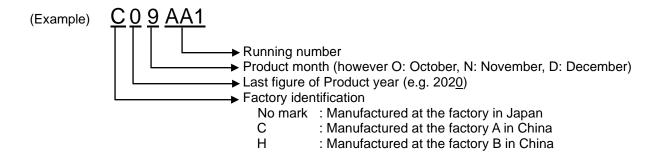

| Package Outlines     2.3.1 Package outlines and PCB Through-hole Pattern                                                       | 2 <del>4</del><br>24 |

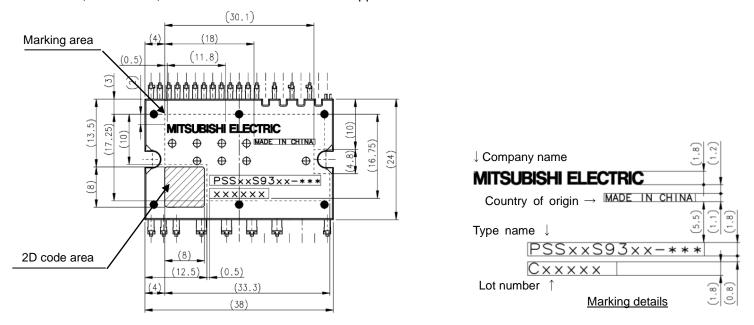

| 2.3.2 Marking                                                                                                                  | 26                   |

| 2.3.3 Terminal Description                                                                                                     |                      |

| 2.4 Mounting Method                                                                                                            | 29                   |

| 2.4.2 Mounting Method and Precautions                                                                                          | 29                   |

| 2.4.3 Soldering Conditions                                                                                                     |                      |

| CHAPTER 3 SYSTEM APPLICATION GUIDANCE                                                                                          |                      |

| 3.1 Application Guidance                                                                                                       |                      |

| 3.1.1 System connection                                                                                                        |                      |

| 3.1.3 Interface Circuit (Example of Optocoupler Isolated Interface)                                                            | 33                   |

| 3.1.4 External SC Protection Circuit with Using Three Shunt Resistors 3.1.5 Circuits of Signal Input Terminals and Fo Terminal | 34                   |

| 3.1.6 Snubber Circuit                                                                                                          |                      |

| 3.1.7 Recommended Wiring Method around Shunt Resistor                                                                          |                      |

| 3.1.9 Parallel operation of DIPIPM                                                                                             |                      |

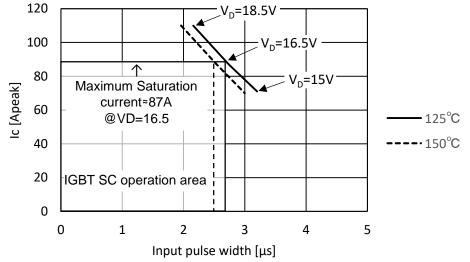

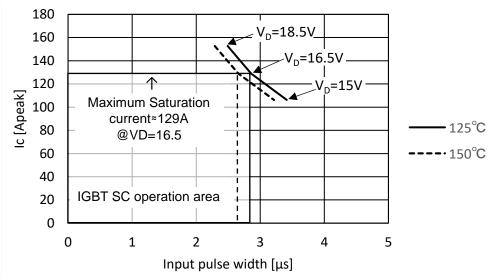

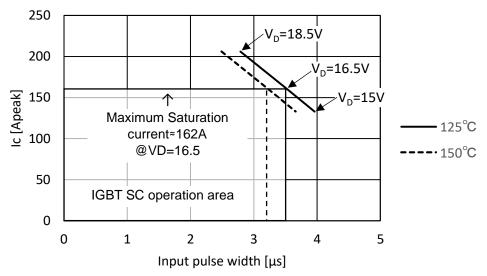

| 3.1.10 SOA of DIPIPM Ver.7                                                                                                     | 39                   |

| 3.1.11 SCSOA                                                                                                                   |                      |

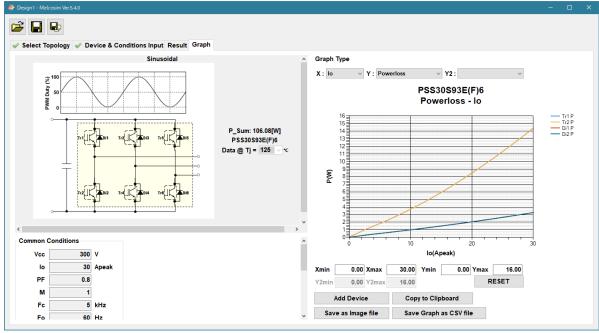

| 3.2 Power Loss and Thermal Dissipation Calculation                                                                             |                      |

| 3.2.1 Power Loss Calculation                                                                                                   | 43                   |

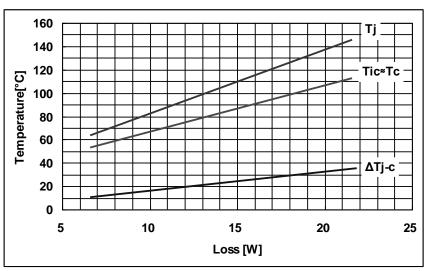

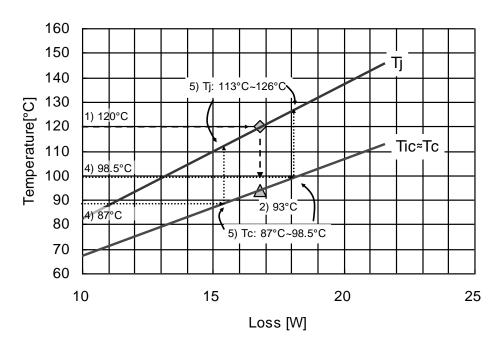

| 3.2.2 Temperature Rise Considerations and Calculation Example                                                                  | 45<br>46             |

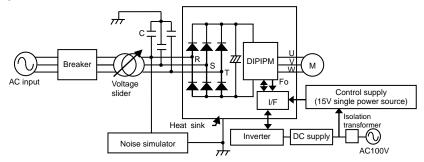

| 3.3 Noise and ESD Withstand Capability                                                                                         |                      |

| 3.3.1 Evaluation Circuit of Noise Withstand Capability                                                                         | 47                   |

| 3.3.2 Countermeasures and Precautions                                                                                          | 47<br>48             |

| CHAPTER 4 Bootstrap Circuit Operation                                                                                          |                      |

| 4.1 Bootstrap Circuit Operation                                                                                                |                      |

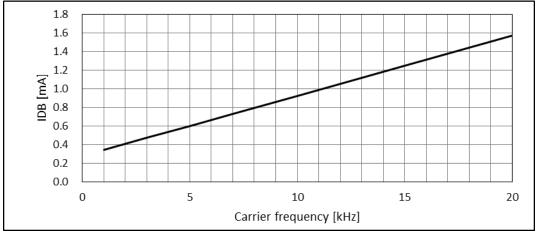

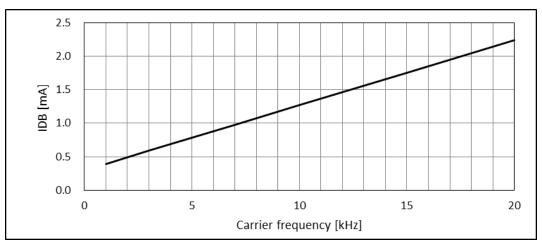

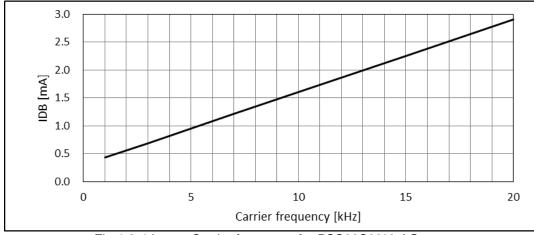

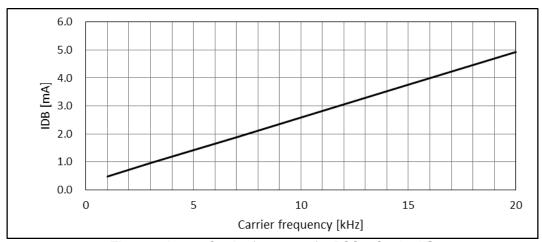

| 4.2 Bootstrap Supply Circuit Current at Switching State                                                                        |                      |

| 4.3 Note for designing the bootstrap circuit                                                                                   |                      |

| 4.4 Initial charging in bootstrap circuit                                                                                      |                      |

| CHAPTER 5 Interface Demo Board                                                                                                 | 54                   |

| 5.1 Super mini DIPIPM Ver.7 Interface Demo Board                                                                               | 54                   |

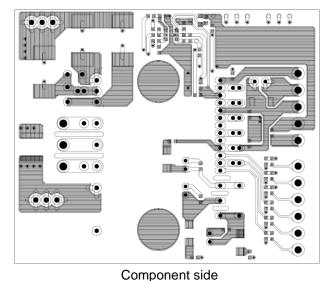

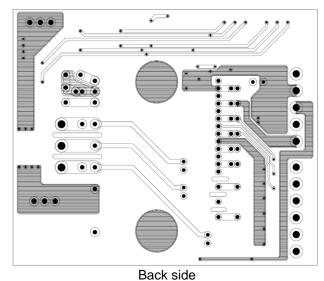

| 5.2 Circuit Schematic, Parts List and Board pattern,                                                                           |                      |

| CHAPTER 6 PACKAGE HANDLING                                                                                                     | 58                   |

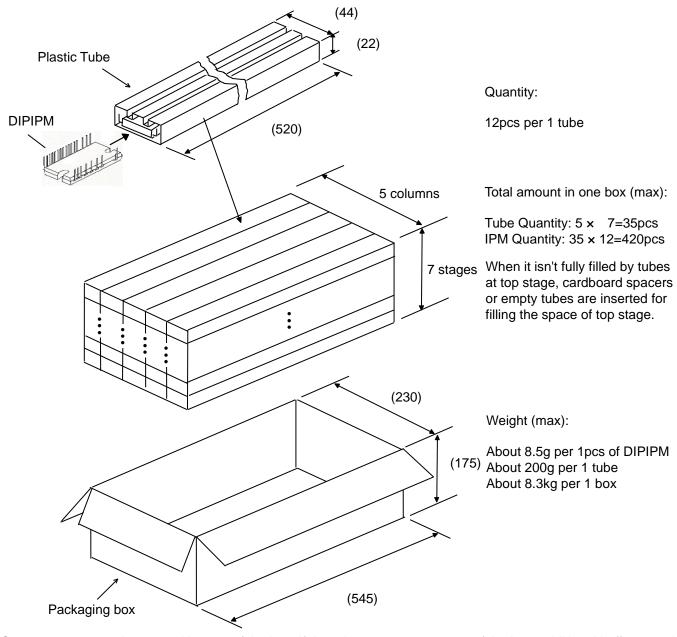

| 6.1 Packaging Specification                                                                                                    | 58                   |

| 6.2 Handling Precautions                                                                                                       | 59                   |

|                                                                                                                                |                      |

#### CHAPTER 1 INTRODUCTION

#### 1.1 Features of Super mini DIPIPM Ver.7

Super Mini DIPIPM Ver.7 (hereinafter called DIPIPM Ver.7) is an ultra-compact intelligent power module with transfer mold package favorable for larger mass production. Power chips, drive and protection circuits are integrated in a module, which makes it easy for AC100-240V class low power motor inverter control.

DIPIPM Ver.7 takes over the functions of conventional DIPIPM Ver.6 (such as incorporating bootstrap diode with resistor, analog temperature signal output), additionally, DIPIPM Ver.7 is improved more.

Main features of DIPIPM Ver.7 are as below.

- Newly developed low noise 7th generation CSTBT are integrated for reducing noise level with same efficiency compared with DIPIPM Ver.6. It achieves system cost reduction for noise suppression parts.

- Operating junction temperature is expanded to 150°C and maximum junction temperature is expanded to 175°C. It can boost up instantaneous over current capability at overload operation.

- The wider shape of terminal root part contributes to improve the terminal strength and to suppress the temperature rise of the soldered part during inverter operation.

- · Expanding line-up up to 40A.

- · Easy to replace from conventional series due to high pin compatibility.

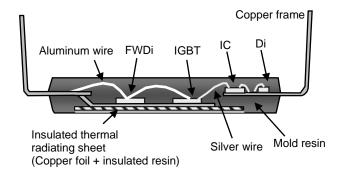

About detailed differences, please refer Section 1.5. Fig.1-1-1 and Fig.1-1-2 show the outline and internal cross-section structure respectively.

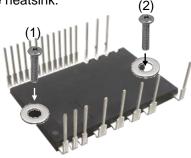

Fig.1-1-1 Package photograph

Fig.1-1-2 Internal cross-section structure

#### 1.2 Functions

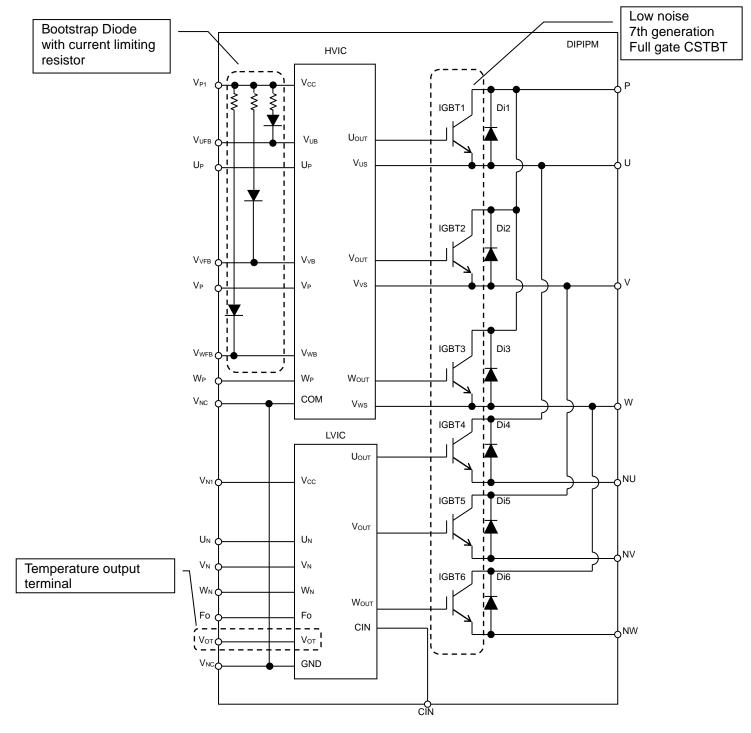

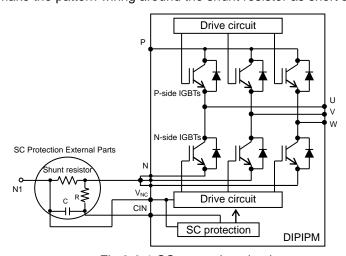

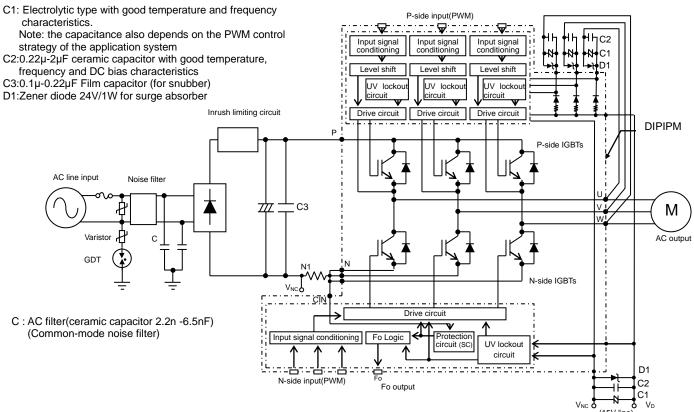

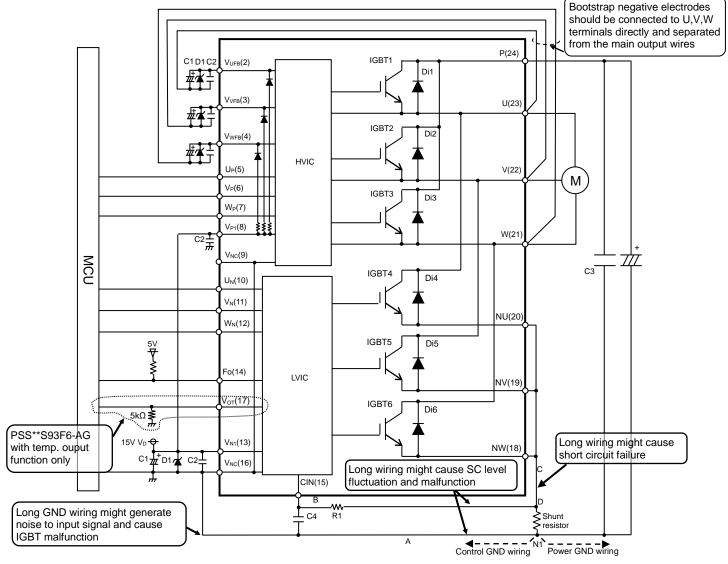

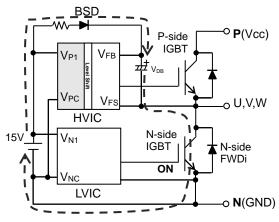

DIPIPM Ver.7 has following functions and inner block diagram as described in Fig.1-2-1.

- For P-side IGBTs:

- Drive circuit:

- High voltage level shift circuit;

- Control supply under voltage (UV) lockout circuit (without fault signal output).

- Built-in bootstrap diode (BSD) with current limiting resistor

- For N-side IGBTs:

- -Drive circuit;

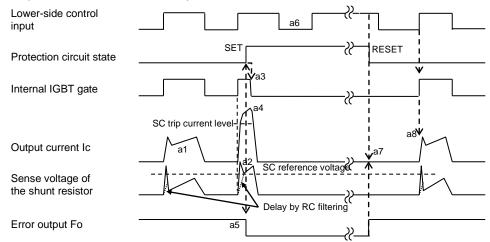

- -Short circuit (SC) protection circuit (by inserting external shunt resistor into main current path)

- -Control supply under voltage (UV) lockout circuit (with fault signal output)

- -Over temperature (OT) protection by monitoring LVIC temperature. (PSS\*\*S93E6-AG series only)

- -Outputting LVIC temperature by analog signal (PSS\*\*S93F6-AG series only)

- Fault Signal Output

- -Corresponding to N-side IGBT SC, N-side UV and OT protection. (OT: PSS\*\*S93E6-AG series only)

- IGBT Drive Supply

- -Single DC15V power supply (in the case of using bootstrap method)

- Control Input Interface

- -Schmitt-triggered 3V, 5V input compatible, high active logic.

- UL recognized

- -UL 1557 File E323585

Fig.1-2-1 Inner block diagram (Temperature output function type)

### 1.3 Target Applications

Motor drives for household electric appliances, such as air conditioners, washing machines, refrigerators Low power industrial motor drive except automotive applications

### 1.4 Product Line-up

Table 1-4-1 DIPIPM Ver.7 Line-up with temperature output function

| Type Name     | IGBT Rating | Motor Rating (Note1) | Isolation Voltage                            |

|---------------|-------------|----------------------|----------------------------------------------|

| PSS15S93F6-AG | 15A/600V    | 0.75kW/220VAC        |                                              |

| PSS20S93F6-AG | 20A/600V    | 1.5kW/220VAC         | V <sub>iso</sub> = 1500Vrms                  |

| PSS30S93F6-AG | 30A/600V    | 2.2kW/220VAC         | (Sine 60Hz, 1min All shorted pins-heat sink) |

| PSS40S93F6-AG | 40A/600V    | 2.2kW/220VAC         | ,                                            |

Table 1-4-2 DIPIPM Ver.7 Line-up with over temperature protection function

| Type Name     | IGBT Rating | Motor Rating (Note1) | Isolation Voltage                            |

|---------------|-------------|----------------------|----------------------------------------------|

| PSS15S93E6-AG | 15A/600V    | 0.75kW/220VAC        |                                              |

| PSS20S93E6-AG | 20A/600V    | 1.5kW/220VAC         | $V_{iso} = 1500 \text{Vrms}$                 |

| PSS30S93E6-AG | 30A/600V    | 2.2kW/220VAC         | (Sine 60Hz, 1min All shorted pins-heat sink) |

| PSS40S93E6-AG | 40A/600V    | 2.2kW/220VAC         | ,                                            |

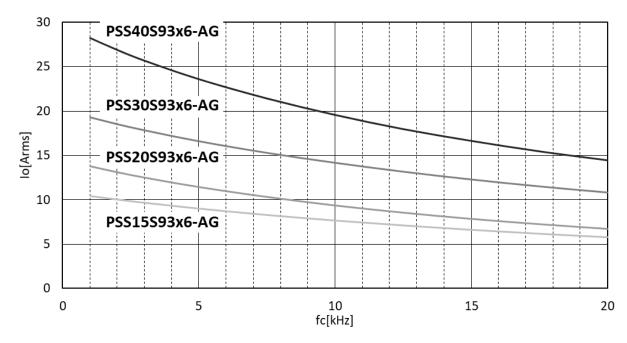

Note 2: The motor ratings are simulation results under following conditions: V<sub>AC</sub>=220V, V<sub>D</sub>=V<sub>DB</sub>=15V, T<sub>C</sub>=100°C, T<sub>j</sub>=125°C, f<sub>PWM</sub>=5kHz, P.F=0.8, motor efficiency=0.75, current ripple ratio=1.05, motor over load 150% 1min.

### 1.5 The Differences between Previous Series and This Series (PSS\*\*S93\*6-AG)

DIPIPM Ver.7 has some differences against conventional series (PS219A\*, PS219B\* and PSS\*S92\*6-AG). Main differences are described as follows. Refer each product datasheets for further information.

Table 1-5-1 Differences of maximum ratings

| Items                             | Symbol            | PS219A*        | PS219B*  | PSS**S92*6-AG | PSS**S93*6-AG            |

|-----------------------------------|-------------------|----------------|----------|---------------|--------------------------|

| iteriis                           | Syllibol          | Ver.4 with BSD | Ver.5    | Ver.6         | Ver.7                    |

| Junction temperature              | Tj                | -30~+150°C     | <b>←</b> | <b>←</b>      | -                        |

| Operation junction temperature    | $T_jop$           | -              | -        | -             | -30~+150°C <sup>1)</sup> |

| Maximum junction temperature      | T <sub>jmax</sub> | -              | -        | -             | Max. 175°C 1)            |

| Module case operation temperature | Tc                | -30~+100°C     | +        | +             | -30~+125°C <sup>1)</sup> |

Note 1: The maximum junction temperature rating of built-in power chips is 175°C(@Tc≤125°C). However, to ensure safe operation of DIPIPM, the average junction temperature should be limited to Tj(Ave)≤150°C (@Tc≤125°C).

#### ■ About 175°C Operation:

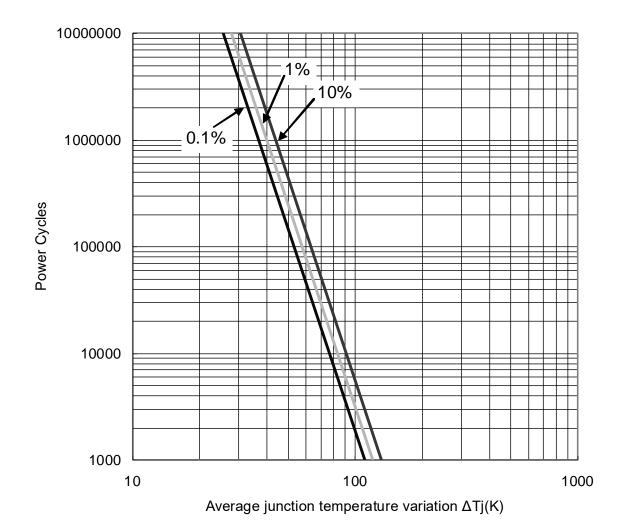

Maximum junction temperature: 175°C is assumed only for instantaneous operation like overload condition. For continuous operation, please design your system at average junction temperature: 150°C or less. It is also necessary to consider its lifetime by the repeated temperature changes.

Table 1-5-2 Differences of specifications and functions

| Items                                                     | PS219A*                           | PS219B*                                       | PSS**S92*6-AG | PSS**S93*6-AG | Ref.             |

|-----------------------------------------------------------|-----------------------------------|-----------------------------------------------|---------------|---------------|------------------|

| items                                                     | Ver.4 with BSD                    | Ver.5                                         | Ver.6         | Ver.7         | Kei.             |

| Built-in bootstrap diodes 1)                              | Built-in                          | Built-in<br>with current<br>limiting resistor | +             | +             | Section<br>4.2   |

| Temperature protection                                    | OT (-T)                           | OT or VOT <sup>2)</sup>                       | +             | +             | Section<br>2.2.4 |

| Dummy terminal<br>(Compare with<br>PS2196*) <sup>3)</sup> | Add one terminal<br>(No. 1-B pin) | +                                             | +             | +             | Section 2.3      |

| N-side IGBT emitter terminal                              | Common / Open                     | Open 3)                                       | +             | +             | 2.3              |

Note 1: Ver.5, Ver.6 and Ver.7 series have built-in bootstrap diode (BSD) with current limiting resistor. So there aren't any limitation about bootstrap capacitance like PS219A\* has (22µF or less in the case of one long pulse initial charging).

Note 2: Temperature protection function of both Ver.5, Ver.6 and Ver.7 series is selectable from two functions. (They have different model numbers.) One is conventional over temperature protection (OT), and the other is LVIC temperature output function (Vot). OT function shutdowns all N-side IGBTs automatically when LVIC temperature exceeds specified value

(For Ver.5 and Ver.6 series: typ.120°C, for Ver.7 series: typ. 140°C). But  $V_{OT}$  function cannot shutdown by itself in that case. So it is necessary for system controller to monitor this  $V_{OT}$  output and shutdown when the temperature reaches the protection level.

Note 3: Because of incorporating bootstrap diodes, a part of package was changed. (Just one dummy terminal was added) But its package size, pin assignment and pin number weren't changed, so the same PCB can be used with small modification when replacing from Super mini DIPIPM Ver.4. (External bootstrap diodes and current limit resistors should be removed in the case of replacing from PS2196\*).

And also if N-side common emitter type was used in former PCB, it is necessary to change wiring from common emitter to open emitter wiring because of both DIPIPM Ver.5 and DIPIPM Ver.6 have open emitter type only.

Table 1-5-4 Differences of specifications and recommended operating conditions (Less than 20A products)

| table 1 6 4 Billerenees of specifications and recommended operating conditions (2005 than 2071) readots) |                   |                     |                    |               |                                                 |

|----------------------------------------------------------------------------------------------------------|-------------------|---------------------|--------------------|---------------|-------------------------------------------------|

| Items                                                                                                    | Symbol            | PS219A*             | PS219B*            | PSS**S92*6-AG | PSS**S93*6-AG                                   |

| items                                                                                                    | Symbol            | Ver.4 with BSD      | Ver.5              | Ver.6         | Ver.7                                           |

| Circuit current for P-side driving                                                                       | ΙD                | Max. 2.80mA         | <b>←</b>           | <del>-</del>  | Max. 3.40mA                                     |

| Circuit current for P-side driving                                                                       | I <sub>DB</sub>   | Max. 0.10mA         | <b>←</b>           | <del>-</del>  | Max. 0.30mA                                     |

| Trip voltage for P-side control supply under voltage protection                                          | UV <sub>DBt</sub> | Min. 7.0V           | <b>←</b>           | <b>←</b>      | Min. 10.0V                                      |

| Reset voltage for P-side control supply under voltage protection                                         | UV <sub>DBr</sub> | Min. 7.0V           | <b>←</b>           | <b>←</b>      | Min. 10.5V                                      |

| Bootstrap Di forward voltage                                                                             | VF                | Typ. 2.8V<br>@100mA | Typ. 1.7V<br>@10mA | +             | <b>←</b>                                        |

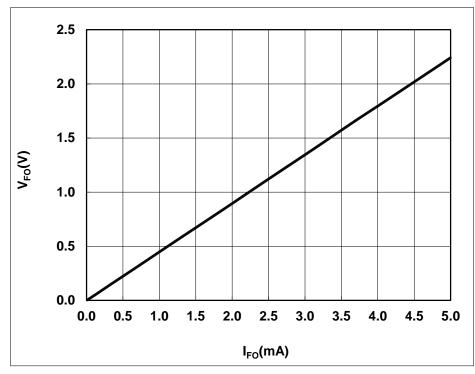

| Fault output current                                                                                     | I <sub>FO</sub>   | Max. 1mA            | +                  | +             | Max. 5mA<br>(Direct coupler drive<br>available) |

| Arm-shoot-through blocking time                                                                          | t <sub>dead</sub> | Min. 1.0µs          | <b>←</b>           | <b>←</b>      | +                                               |

| Allowable minimum input pulse                                                                            | PWIN(on)          | Min. 0.5µs          | Min. 0.7µs         | <del>-</del>  | Min. 0.7μs <sup>1)</sup>                        |

| width                                                                                                    | PWIN(off)         | Min. 0.5µs          | Min. 0.7µs         | <del>(</del>  | Min. 0.7μs <sup>1)</sup>                        |

Table 1-5-5 Differences of specifications and recommended operating conditions (More than 30A products)

|                                                                  |                   | PSS**S92*6-AG                                               | PSS**S93*6-AG                             |

|------------------------------------------------------------------|-------------------|-------------------------------------------------------------|-------------------------------------------|

| Items                                                            | Symbol            | Ver.6                                                       | Ver.7                                     |

| Circuit current for P-side driving                               | ID                | Max. 3.40mA                                                 | +                                         |

| Circuit current for P-side driving                               | I <sub>DB</sub>   | Max. 0.30mA                                                 | +                                         |

| Trip voltage for P-side control supply under voltage protection  | UV <sub>DBt</sub> | Min. 10.0V                                                  | +                                         |

| Reset voltage for P-side control supply under voltage protection | UV <sub>DBr</sub> | Min. 10.5V                                                  | +                                         |

| Bootstrap Di forward voltage                                     | VF                | Typ. 1.3V@10mA                                              | <b>←</b>                                  |

| Fault output current                                             | I <sub>FO</sub>   | Max. 1mA                                                    | Max. 5mA (Direct coupler drive available) |

| Arm-shoot-through blocking time                                  | t <sub>dead</sub> | 30,35A: Min.2.0µs                                           | 30A: Min 1.0µs<br>40A: Min.1.5µs          |

| Allowable minimum input pulse                                    | PWIN(on)          | Min. 0.7µs                                                  | Min. 0.7μs <sup>1)</sup>                  |

| Allowable minimum input pulse width                              | PWIN(off)         | Due to current rating <sup>2)</sup><br>Refer each datasheet | Min. 0.7μs <sup>1)</sup>                  |

Note 1: When inputting shorter pulse than PWIN(on), DIPIPM might not make response.

DIPIPM might make delayed response or no response for the input signal with off pulse width less than PWIN(off). Moreover, in case of rated current or more, DIPIPM might make delayed response even for input signal with off pulse more than PWIN(off), Please refer below about delayed response. Please refer below about delayed response.

Note 2: IPM might make delayed response or no response for the input signal with off pulse width less than PWIN(off). Please refer below about delayed response. (Ver.6 30~35A products only).

In case of 5~20A products IPM might not make response. Refer the datasheet for each product.

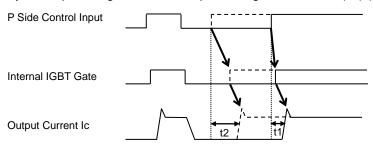

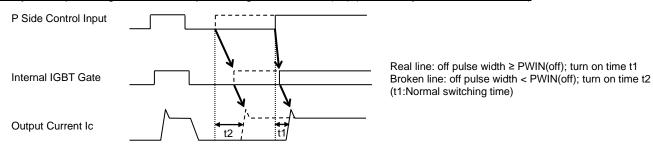

#### Delayed Response against Shorter Input Off Signal than PWIN(off) (P-side only)

Real line: off pulse width > PWIN(off); turn on time t1 Broken line: off pulse width < PWIN(off); turn on time t2 (t1:Normal switching time)

Table 1-5-6 Improved points of Ver.7 series from former products (e.g. Comparison of each 15A products)

| Items                                  | Symbol                        | PS219A4        | PS219C4  | PSS15S92*6-AG              | PSS15S93*6-AG    |

|----------------------------------------|-------------------------------|----------------|----------|----------------------------|------------------|

| items                                  | Symbol                        | Ver.4 with BSD | Ver.5    | Ver.6                      | Ver.7            |

| Saturation valtage                     | V <sub>CE(sat)</sub> 1)       | Max. 2.0V @15A | <b>←</b> | Max. 2.05V @15A            | Max. 2.05V @15A  |

| Saturation voltage                     | V CE(sat)                     | -              | -        | Max. 1.10V @1.5A           | Max. 1.10V @1.5A |

| Short circuit trip level               | V <sub>SC(ref)</sub>          | 0.48V±0.05V    | <b>←</b> | 0.48V±0.025V <sup>2)</sup> | +                |

| Over temperature protection Trip level | OT <sub>t</sub> <sup>3)</sup> | Typ.120°C      | <b>←</b> | <b>←</b>                   | Typ.140°C        |

- Note 1: V<sub>CE(sat)</sub> specification at one tenth of the rated current is added since Ver.6 and Ver.7 series to care room air conditioner system efficiency at low power operation which will affect APF(annual performance factor).

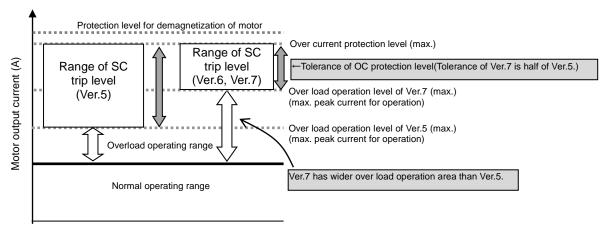

- Note 2: Short circuit trip level tolerance of Ver.6 is improved to 0.48±5%. By this improvement, Ver.6 has wider overload operating range. If short circuit protection is applied to the protection for demagnetization of motor, wider overload operating range can be realized due to improve trip level tolerance as in Fig.1-5-1.

- Note 3: Condition: V<sub>D</sub>=15V, detected by LVIC temperature.

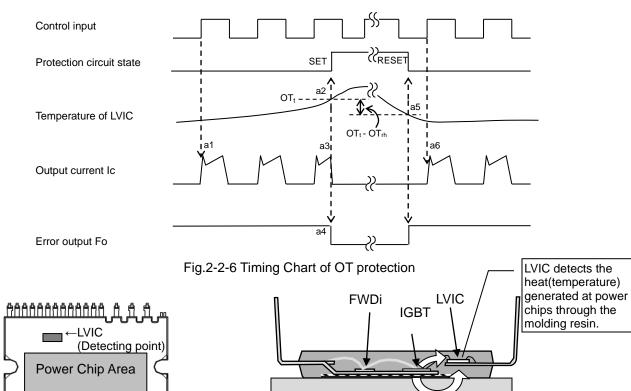

When the LVIC temperature exceeds the OT protection trip level (OT<sub>t</sub>), all N-side IGBTs turn OFF in spite of control input condition and Fo outputs. For Ver.7 series, the OT protection trip level is also expanded to typ.140°C from typ. 120°C of conventional series because the maximum rating of junction temperature Tj and case temperature Tc are expanded. In that case if the heatsink dropped off or fixed loosely, don't reuse that DIPIPM. There is a possibility that junction temperature of power chips exceeded its maximum junction temperature (For Ver.5 and Ver.6 series: 150°C, for Ver.7 series: 175°C).

Fig.1-5-1 Comparison of fluctuation of short circuit trip level

For more detail and the other characteristics, please refer the datasheet for each product.

#### CHAPTER 2 SPECIFICATIONS AND CHARACTERISTICS

### 2.1 Super Mini DIPIPM Ver.7 Specifications

DIPIPM Ver.7 specifications are described below by using PSS15S93\*6-AG (15A/600V) as an example. Please refer to respective datasheets for the detailed description of other types.

#### 2.1.1 Maximum Ratings

The maximum ratings of PSS15S93\*6-AG (15A/600V) are shown in Table 2-1-1. (Tj = 25°C, unless otherwise noted)

Table 2-1-1 Maximum Ratings

#### INVERTER PART

| Symbol                 | Parameter                          | Condition                            | Ratings  | Unit |     |

|------------------------|------------------------------------|--------------------------------------|----------|------|-----|

| Vcc                    | Supply voltage                     | Applied between P-NU,NV,NW           | 450      | V    | (1) |

| V <sub>CC(surge)</sub> | Supply voltage (surge)             | Applied between P-NU,NV,NW           | 500      | V    | (2) |

| Vces                   | Collector-emitter voltage          |                                      | 600      | V    | (3) |

| ±l <sub>C</sub>        | Each IGBT collector current        | T <sub>C</sub> = 25°C (Note1)        | 15       | Α    | (4) |

| ±I <sub>CP</sub>       | Each IGBT collector current (peak) | T <sub>C</sub> = 25°C, less than 1ms | 30       | Α    |     |

| T <sub>jop</sub>       | Operating Junction temperature     | Continuous operation (Note2)         | -30~+150 | °C   | 1   |

| T <sub>jmax</sub>      | Maximum Junction temperature       | Temporally operation (e.g. overload) | 175      | °C   | (5) |

Note1: Pulse width and period are limited due to junction temperature.

Note2: The maximum junction temperature rating of built-in power chips is 175°C(@Tc≤125°C). However, to ensure safe operation of DIPIPM, the average junction temperature should be limited to Tj(Ave)≤150°C (@Tc≤125°C).

#### **CONTROL (PROTECTION) PART**

| Symbol          | Parameter                     | Condition                                                                                                                            | Ratings                  | Unit |

|-----------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|

| $V_D$           | Control supply voltage        | Applied between V <sub>P1</sub> -V <sub>NC</sub> , V <sub>N1</sub> -V <sub>NC</sub>                                                  | 20                       | V    |

| V <sub>DB</sub> | Control supply voltage        | Applied between V <sub>UFB</sub> -U, V <sub>VFB</sub> -V, V <sub>WFB</sub> -W                                                        | 20                       | V    |

| V <sub>IN</sub> | Input voltage                 | Applied between U <sub>P</sub> , V <sub>P</sub> , W <sub>P</sub> , U <sub>N</sub> , V <sub>N</sub> , W <sub>N</sub> -V <sub>NC</sub> | -0.5~V <sub>D</sub> +0.5 | V    |

| V <sub>FO</sub> | Fault output supply voltage   | Applied between Fo-V <sub>NC</sub>                                                                                                   | -0.5~V <sub>D</sub> +0.5 | V    |

| I <sub>FO</sub> | Fault output current          | Fo terminal sink current                                                                                                             | 5                        | mA   |

| Vsc             | Current sensing input voltage | Applied between CIN-V <sub>NC</sub>                                                                                                  | -0.5~V <sub>D</sub> +0.5 | V    |

#### TOTAL SYSTEM

| Symbol                | Parameter                                                                  | Condition                                                                                           | Ratings  | Unit             | 1     |

|-----------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------|------------------|-------|

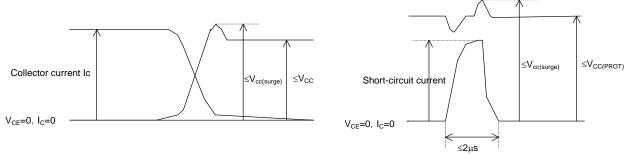

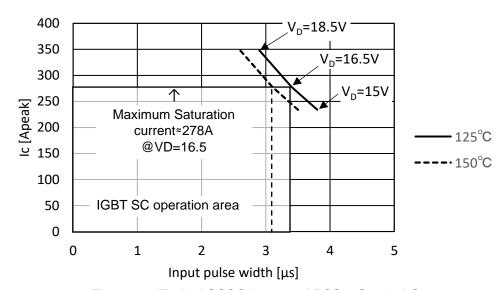

| V <sub>CC(PROT)</sub> | Self protection supply voltage limit (Short circuit protection capability) | V <sub>D</sub> = 13.5~16.5V, Inverter Part<br>T <sub>j</sub> = 150°C, non-repetitive, less than 2μs | 400      | V                | ← (6) |

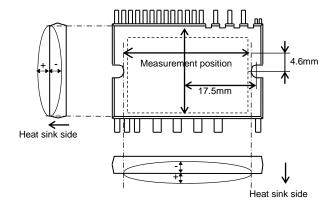

| Tc                    | Module case operation temperature                                          | Measurement point of Tc is provided in the following figure                                         | -30~+125 | °C               | 1     |

| T <sub>stg</sub>      | Storage temperature                                                        |                                                                                                     | -40~+125 | °C               | 1     |

| V <sub>iso</sub>      | Isolation voltage                                                          | 60Hz, Sinusoidal, AC 1min,<br>between connected all pins and heat sink plate                        | 1500     | V <sub>rms</sub> | (7)   |

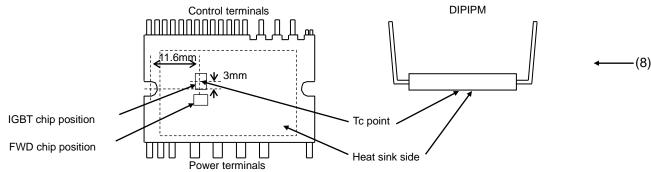

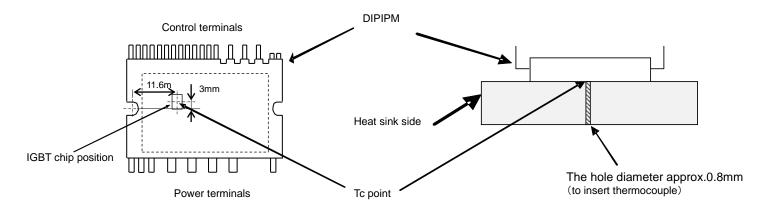

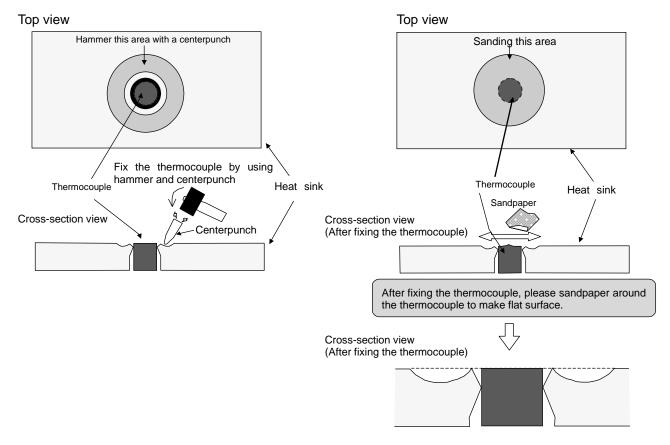

Tc measurement position

(1) Vcc The maximum voltage can be biased between P-N. A voltage suppressing circuit such as a brake circuit is necessary if P-N voltage exceeds this value.

(2) Vcc(surge) The maximum P-N surge voltage in switching state. If P-N voltage exceeds this voltage, a snubber circuit is necessary to absorb the surge under this voltage.

(3) V<sub>CES</sub> The maximum sustained collector-emitter voltage of built-in IGBT.

(4) +/-lc The allowable current flowing into collect electrode (@Tc=25°C). Pulse width and period are limited due to junction temperature Ti.

(5) Tj The maximum junction temperature rating is 175°C. But for safe operation, it is recommended to limit the average junction temperature up to 150°C(@Tc≤125°C). Repetitive temperature variation ΔTj affects the life time of power cycle, so refer lifetime curves for safety design.

(6) Vcc(prot) The maximum supply voltage for turning off IGBT safely in the case of an SC or OC fault. The power chip might be damaged if supply voltage exceeds this specification.

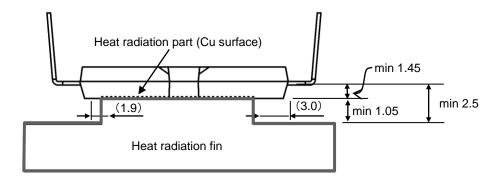

(7) Isolation voltage

Isolation voltage of Super mini DIPIPM is the voltage between all shorted pins and copper surface of DIPIPM. The maximum rating of isolation voltage of Super mini DIPIPM is 1500Vrms. But if such as convex shape heat radiation fin will be used for enlarging clearance between outer terminals and heat radiation fin (2.5mm or more is recommended), it is able to correspond isolation voltage 2500Vrms. Super mini DIPIPM is recognized by UL at the condition 2500Vrms with pedestal shape heat radiation fin.

Fig.2-1-1 In the case of using pedestal fin (unit: mm)

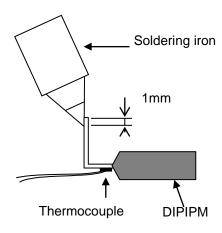

(8) Tc position Tc (case temperature) is defined to be the temperature just beneath the specified power chip. Please mount a thermocouple on the heat sink surface at the defined position to get accurate temperature information. Due to the control schemes such different control between P and N-side, there is the possibility that highest Tc point is different from above point. In such cases, it is necessary to change the measuring point to that under the highest power chip.

#### [Power chip position]

Fig.2-1-2 indicates the position of each power chips. (This figure is the view from laser marked side.)

Fig.2-1-2 Power chip position

#### 2.1.2 Thermal Resistance

Table 2-1-2 shows the thermal resistance of PSS15S93\*6-AG (15A/600V). (Tj = 25°C, unless otherwise noted)

Table 2-1-2 Thermal resistance of PSS15S93\*6-AG (15A/600V)

#### THERMAL RESISTANCE

| Symbol                | Doromotor                | Condition                           |      | Unit |      |      |

|-----------------------|--------------------------|-------------------------------------|------|------|------|------|

| Symbol                | Parameter                | Condition                           | Min. | Тур. | Max. | Unit |

| $R_{th(j-c)Q}$        | Junction to case thermal | Inverter IGBT part (per 1/6 module) | -    | -    | 3.7  | K/W  |

| R <sub>th(i-c)F</sub> | resistance (Note)        | Inverter FWDi part (per 1/6 module) | -    | -    | 3.9  | K/W  |

Note: Grease with good thermal conductivity and long-term endurance should be applied evenly with about +100µm~+200µm on the contacting surface of DIPIPM and heat sink. The contacting thermal resistance between DIPIPM case and heat sink Rth(c-f) is determined by the thickness and the thermal conductivity of the applied grease. For reference, Rth(c-f) is about 0.3K/W (per 1/6 module, grease thickness: 20µm, thermal conductivity: 1.0W/m•K).

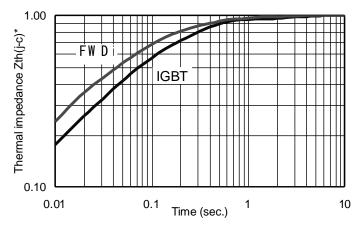

The above data shows the thermal resistance between chip junction and case at steady state. The thermal resistance goes into saturation in about 10 seconds. The unsaturated thermal resistance is called as transient thermal impedance which is shown in Fig.2-1-3.  $Zth(j-c)^*$  is the normalized value of the transient thermal impedance.  $(Zth(j-c)^* = Zth(j-c) / Rth(j-c)max)$

For example, the IGBT transient thermal impedance of PSS15S93\*6-AG in 0.3s is 3.7x0.8=2.96K/W. The transient thermal impedance isn't used for constantly current, but for short period current (ms order). (e.g. In the cases at motor starting, at motor lock···)

Fig.2-1-3 Typical transient thermal impedance

#### 2.1.3 Electric Characteristics and Recommended Conditions

Table 2-1-3 shows the typical static characteristics and switching characteristics of PSS15S93\*6-AG(15A/600V). ( $T_i = 25$ °C, unless otherwise noted)

Table 2-1-3 Static characteristics and switching characteristics of PSS15S93\*6-AG(15A/600V)

INVERTER PART

| INVENTER FACT      |                                           |                                                                      |                                               |        |      |      |       |  |

|--------------------|-------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|--------|------|------|-------|--|

| Symbol             | Parameter                                 | Condition                                                            | 20                                            | Limits |      |      | Unit  |  |

| Syllibol           | Farameter                                 | Condition                                                            |                                               | Min.   | Тур. | Max. | Offic |  |

|                    |                                           |                                                                      | I <sub>C</sub> = 15A , T <sub>j</sub> = 25°C  | -      | 1.70 | 2.05 |       |  |

| $V_{CE(sat)}$      | Collector-emitter saturation voltage      | $V_{D} = V_{DB} = 15V, V_{IN} = 5V$                                  | I <sub>C</sub> = 15A , T <sub>j</sub> = 125°C | -      | 1.90 | 2.25 | V     |  |

|                    | voltage                                   |                                                                      | I <sub>C</sub> = 1.5A , T <sub>j</sub> = 25°C | -      | 0.90 | 1.10 |       |  |

| V <sub>EC</sub>    | FWDi forward voltage                      | V <sub>IN</sub> = 0V, -I <sub>C</sub> = 15A                          |                                               | -      | 1.75 | 2.25 | V     |  |

| t <sub>on</sub>    |                                           |                                                                      |                                               | 0.95   | 1.55 | 2.25 | μs    |  |

| t <sub>C(on)</sub> |                                           | $V_{CC} = 300 \text{V}, V_D = V_{DB} = 15 \text{V}$                  |                                               | -      | 0.40 | 0.65 | μs    |  |

| t <sub>off</sub>   | Switching times                           | I <sub>C</sub> = 15A, T <sub>j</sub> = 125°C, V <sub>IN</sub> = 0↔5V |                                               | -      | 1.75 | 2.45 | μs    |  |

| $t_{C(off)}$       | 7                                         | Inductive Load (upper-lower arr                                      | n)                                            | -      | 0.15 | 0.30 | μs    |  |

| t <sub>rr</sub>    |                                           |                                                                      |                                               | -      | 0.30 | -    | μs    |  |

|                    | Collector-emitter cut-off                 | V -V                                                                 | T <sub>j</sub> = 25°C                         | -      | -    | 1    | mA    |  |

| ICES               | current V <sub>CE</sub> =V <sub>CES</sub> | T <sub>j</sub> = 125°C                                               | -                                             | -      | 10   | IIIA |       |  |

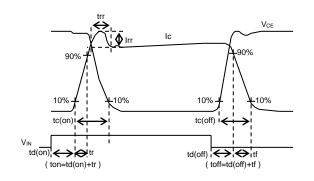

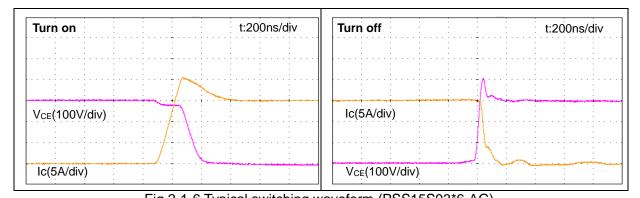

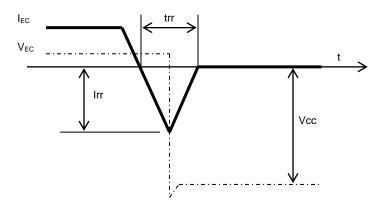

Switching time definition and performance test method are shown in Fig.2-1-4 and 2-1-5. Switching characteristics are measured by half bridge circuit with inductance load.

Fig.2-1-4 Switching time definition

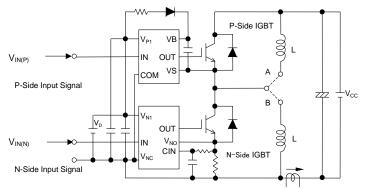

Fig.2-1-5 Evaluation circuit (inductive load) Short A for N-side IGBT, and short B for P-side IGBT evaluation

Fig.2-1-6 Typical switching waveform (PSS15S93\*6-AG)

Conditions: Vcc=300V, V<sub>D</sub>=V<sub>DB</sub>=15V, Tj=125°C, Ic=15A, Inductive load half-bridge circuit

Table 2-1-4 shows the typical control part characteristics of PSS15S93\*6-AG(15A/600V). (Tj =  $25^{\circ}$ C, unless otherwise noted)

Table 2-1-4 Control (Protection) characteristics of PSS15S93\*6-AG(15A/600V)

**CONTROL (PROTECTION) PART**

| Symbol               | Parameter                               | Condition                                                                                                                            |                                          |       | Limits |       | Unit |

|----------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|--------|-------|------|

| Symbol               | Parameter                               | Cond                                                                                                                                 | IUON                                     | Min.  | Тур.   | Max.  | Unit |

|                      |                                         | Total of V <sub>P1</sub> -V <sub>NC</sub> , V <sub>N1</sub> -V <sub>NC</sub>                                                         | V <sub>D</sub> =15V, V <sub>IN</sub> =0V | -     | -      | 3.40  |      |

| I <sub>D</sub>       | Circuit current                         | IOIAI OI VP1-VNC, VN1-VNC                                                                                                            | $V_D=15V$ , $V_{IN}=5V$                  | 1     | -      | 3.40  | mA   |

|                      | Circuit current                         | Each part of V <sub>UFB</sub> -U,                                                                                                    | $V_D=V_{DB}=15V$ , $V_{IN}=0V$           | -     | -      | 0.30  | IIIA |

| I <sub>DB</sub>      |                                         | V <sub>VFB</sub> -V, V <sub>WFB</sub> -W                                                                                             | $V_D=V_{DB}=15V$ , $V_{IN}=5V$           | -     | -      | 0.30  |      |

| $V_{SC(ref)}$        | Short circuit trip level                | $V_D = 15V$                                                                                                                          | (Note 1)                                 | 0.455 | 0.480  | 0.505 | V    |

| $UV_DBt$             | P-side Control supply                   |                                                                                                                                      | Trip level                               | 10.0  | -      | 12.0  | V    |

| $UV_DBr$             | under-voltage protection(UV)            | T <125°C                                                                                                                             | Reset level                              | 10.5  | -      | 12.5  | V    |

| $UV_Dt$              | N-side Control supply                   | T <sub>j</sub> ≤125°C                                                                                                                | Trip level                               | 10.3  | -      | 12.5  | V    |

| $UV_Dr$              | under-voltage protection(UV)            |                                                                                                                                      | Reset level                              | 10.8  | -      | 13.0  | V    |

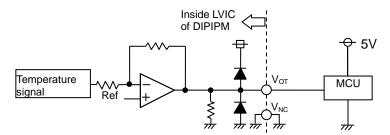

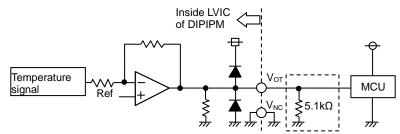

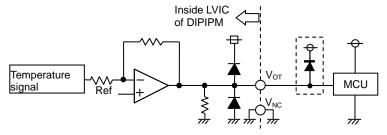

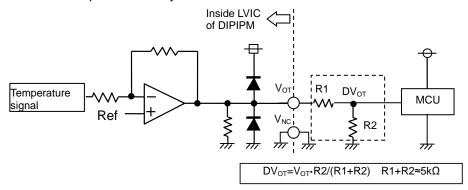

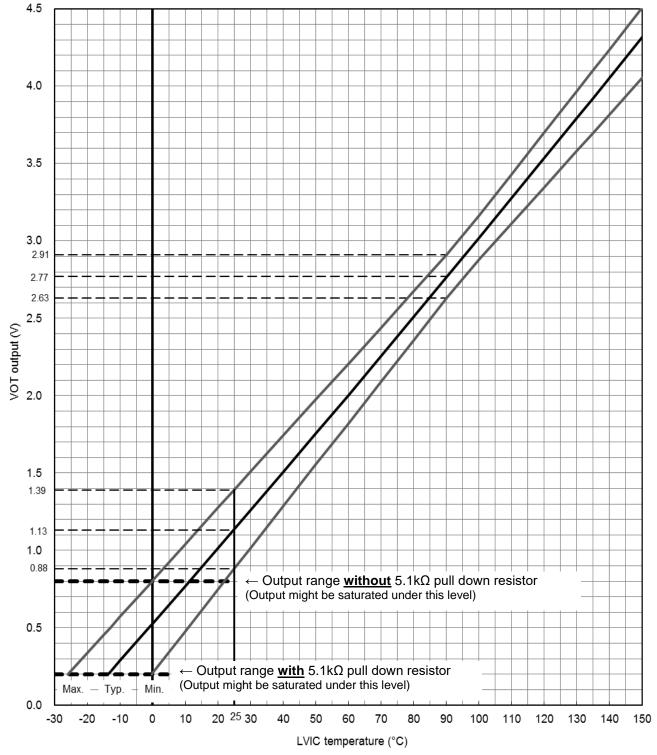

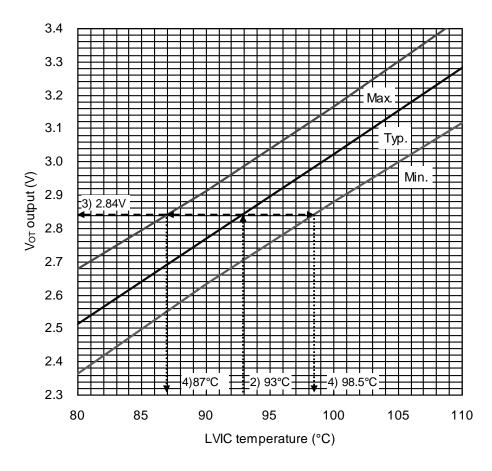

| V <sub>OT</sub>      | Temperature output                      | Pull down R=5.1kΩ (Note 2)                                                                                                           | LVIC Temperature=90°C                    | 2.63  | 2.77   | 2.91  | V    |

| VOT                  | (PSS15S93F6-AG only) (Note5)            |                                                                                                                                      | LVIC Temperature=25°C                    | 0.88  | 1.13   | 1.39  | V    |

| OT <sub>t</sub>      | Overt temperature protection            | V <sub>D</sub> = 15V                                                                                                                 | Trip level                               | 130   | 140    | 150   | °C   |

| OT <sub>rh</sub>     | (PSS15S93E6-AG only)<br>(Note3) (Note5) | Detect LVIC temperature                                                                                                              | Hysteresis of trip-reset                 | -     | 10     | -     | °C   |

| V <sub>FOH</sub>     | Coult output valtage                    | V <sub>SC</sub> = 0V, F <sub>O</sub> terminal pulled up                                                                              | to 5V by 10kΩ                            | 4.9   | -      | -     | V    |

| $V_{FOL}$            | Fault output voltage                    | $V_{SC} = 1V$ , $I_{FO} = 1mA$                                                                                                       |                                          | -     | -      | 0.95  | V    |

| t <sub>FO</sub>      | Fault output pulse width                |                                                                                                                                      | (Note 4)                                 | 20    | -      | -     | μs   |

| I <sub>IN</sub>      | Input current                           | $V_{IN} = 5V$                                                                                                                        |                                          | 0.70  | 1.00   | 1.50  | mA   |

| $V_{th(on)}$         | ON threshold voltage                    | Applied between U <sub>P</sub> , V <sub>P</sub> , W <sub>P</sub> , U <sub>N</sub> , V <sub>N</sub> , W <sub>N</sub> -V <sub>NC</sub> |                                          | -     | 1.70   | 2.35  |      |

| $V_{th(off)}$        | OFF threshold voltage                   |                                                                                                                                      |                                          | 0.70  | 1.20   | -     | V    |

| $V_{\text{th(hys)}}$ | ON/OFF threshold hysteresis voltage     |                                                                                                                                      |                                          | 0.25  | 0.50   | -     |      |

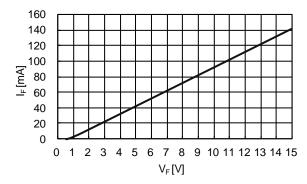

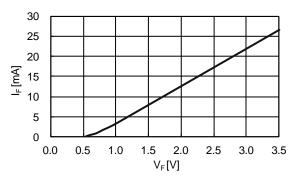

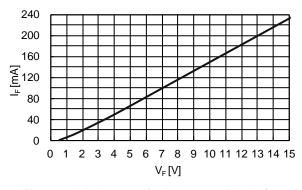

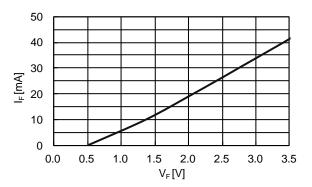

| $V_{F}$              | Bootstrap Di forward voltage            | I <sub>F</sub> =10mA including voltage drop b                                                                                        | by limiting resistor                     | 1.1   | 1.7    | 2.3   | V    |

| R                    | Built-in limiting resistance            | Included in bootstrap Di                                                                                                             |                                          | 80    | 100    | 120   | Ω    |

Note 1 : SC protection works only for N-side IGBT. Please select the external shunt resistance such that the SC trip-level is less than 1.7 times of the current rating.

# \*) Characteristic of Bootstrap Di (V<sub>F</sub>, R) are different between the rated current. For more detail, refer the datasheet for each product.

<sup>2 :</sup> For temperature output type, DIPIPM don't shutdown IGBTs and output fault signal automatically when temperature rises excessively. When temperature exceeds the protective level that user defined, controller (MCU) should stop the DIPIPM. Temperature of LVIC vs. VOT output characteristics is described in Fig. 3.

<sup>3 :</sup> When the LVIC temperature exceeds OT trip temperature level(OT<sub>t</sub>), OT protection works and Fo outputs. In that case if the heat sink dropped off or fixed loosely, don't reuse that DIPIPM. (There is a possibility that junction temperature of power chips exceeded maximum Tjop (175°C).

<sup>4 :</sup> Fault signal Fo outputs when SC, UV or OT protection works. Fo pulse width is different for each protection modes. At SC failure, Fo pulse width is a fixed width (=minimum 20μs), but at UV or OT failure, Fo outputs continuously until recovering from UV or OT state. (But minimum Fo pulse width is 20μs.)

<sup>5:</sup> It is necessary to select from temperature output function or over temperature protection about temperature protection.

Their part numbers are different. (e.g. PSS15S93<u>F</u>6-AG is the type with temperature output function and PSS15S93<u>F</u>6-AG is the type with over temperature protection.)

Recommended operating conditions of PSS15S93\*6-AG (15A/600V) are given in Table 2-1-5. ( $T_i = 25^{\circ}C$ , unless otherwise noted)

Although these conditions are the recommended but not the necessary ones, it is highly recommended to operate the modules within these conditions so as to ensure DIPIPM safe operation.

Table 2-1-5 Recommended operating conditions of PSS15S93\*6-AG (15A/600V)

#### RECOMMENDED OPERATIONAL CONDITIONS

| Cymbal                         | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Condition                                                                           |      | Limits |      | Unit  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|--------|------|-------|

| Symbol                         | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Condition                                                                           | Min. | Тур.   | Max. | Offit |

| V <sub>CC</sub>                | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Applied between P-NU, NV, NW                                                        | 0    | 300    | 400  | V     |

| $V_D$                          | Control supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Applied between V <sub>P1</sub> -V <sub>NC</sub> , V <sub>N1</sub> -V <sub>NC</sub> | 13.5 | 15.0   | 16.5 | V     |

| $V_{DB}$                       | Control supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Applied between V <sub>UFB</sub> -U, V <sub>VFB</sub> -V, V <sub>WFB</sub> -W       | 13.0 | 15.0   | 18.5 | V     |

| $\Delta V_D$ , $\Delta V_{DB}$ | Control supply variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                     | -1   | -      | +1   | V/µs  |

| t <sub>dead</sub>              | Arm shoot-through blocking time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | For each input signal                                                               | 1.0  | -      | -    | μs    |

| f <sub>PWM</sub>               | PWM input frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>C</sub> ≤ 125°C, T <sub>j</sub> ≤ 150°C                                      | -    | -      | 20   | kHz   |

| PWIN(on)                       | National control of the state o | (Al-4- 4)                                                                           | 0.7  | -      | -    |       |

| PWIN(off)                      | Minimum input pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (Note 1)                                                                            | 0.7  | -      | -    | μs    |

| V <sub>NC</sub>                | V <sub>NC</sub> variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Between V <sub>NC</sub> -NU, NV, NW (including surge)                               | -5.0 | -      | +5.0 | V     |

| Tj                             | Junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     | -30  | -      | 150  | °C    |

Note 1: When inputting shorter pulse than PWIN(on), DIPIPM might not make response.

#### Delayed Response against Shorter Input Off Signal than PWIN(off) (P-side only, above rated current)

# \*) Some specifications are different between the rated current. For more detail, please refer the datasheet for each product.

About Control supply variation

If high frequency noise superimposed to the control supply line, IC malfunction might happen and cause DIPIPM erroneous operation. To avoid such problem, line ripple voltage should meet the following specifications:

dV/dt ≤ +/-1V/µs, Vripple≤2Vp-p

<sup>2:</sup> DIPIPM might make delayed response or no response for the input signal with off pulse width less than PWIN(off). Moreover, in case of rated current or more, DIPIPM might make delayed response even for input signal with off pulse more than PWIN(off), Please refer below about delayed response.

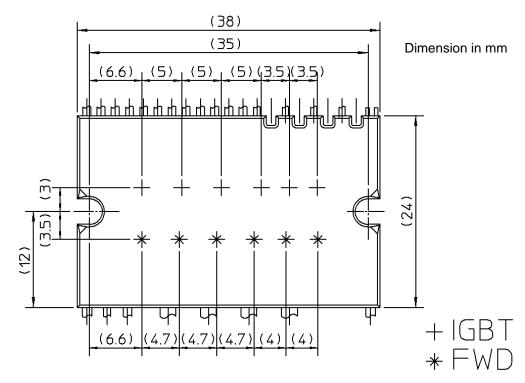

#### 2.1.4 Mechanical Characteristics and Ratings

The mechanical characteristics and ratings are shown in Table 2-1-6. Please refer to Section 2.4 for the detailed mounting instruction of DIPIPM Ver.7.

Table 2-1-6 Mechanical characteristics and ratings of PSS15S93\*6-AG (15A/600V)

#### **MECHANICAL CHARACTERISTICS AND RATINGS**

| Parameter                 | Condition                                                             | Reference                       | Limits |      | Unit |       |

|---------------------------|-----------------------------------------------------------------------|---------------------------------|--------|------|------|-------|

| Parameter                 | Condition                                                             | Reference                       | Min.   | Тур. | Max. | Unit  |

| Mounting torque           | Mounting screw: M3 (Note 1)                                           | JEITA-ED-4701<br>Method 402 II  | 0.59   | 0.69 | 0.78 | N∙m   |

| Terminal pulling strength | Control terminal: Load 5N<br>Power terminal: Load 10N                 | JEITA-ED-4701<br>Method 402 I   | 10     | -    | -    | s     |

| Terminal bending strength | Control terminal: Load 2.5N<br>Power terminal: Load 5N<br>90deg. bend | JEITA-ED-4701<br>Method 402 III | 2      | -    | -    | times |

| Weight                    |                                                                       |                                 | 1      | 8.5  | ı    | g     |

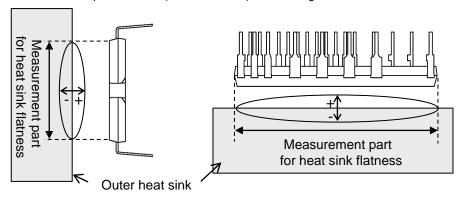

| Heat-sink flatness        | (Note 2)                                                              |                                 | -50    | -    | 100  | μm    |

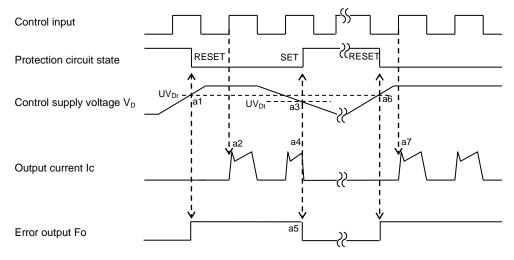

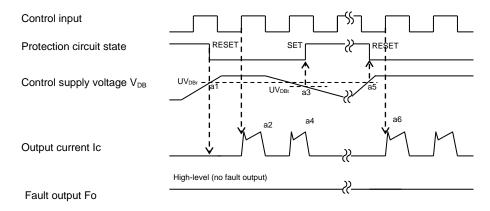

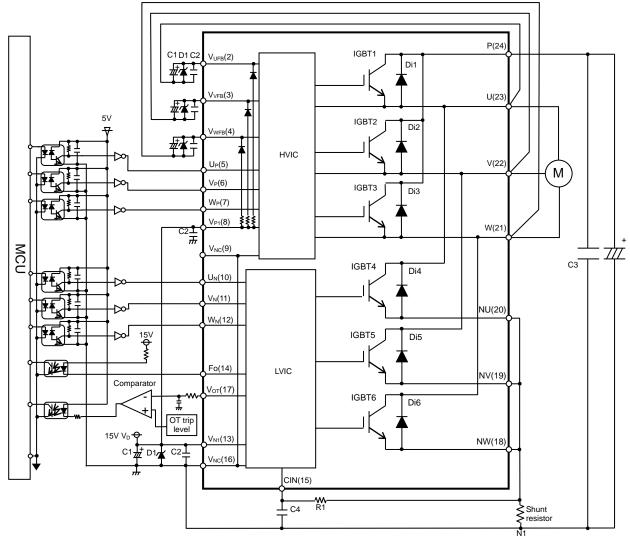

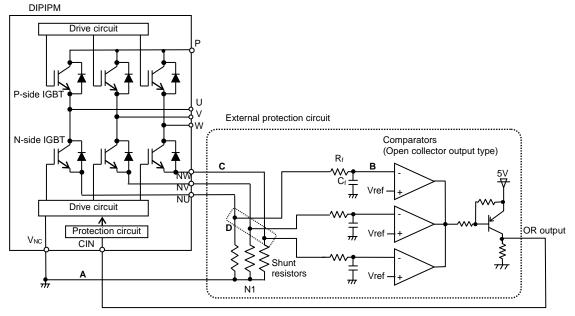

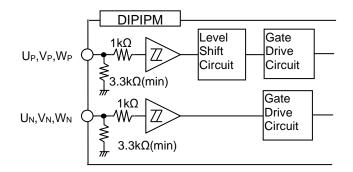

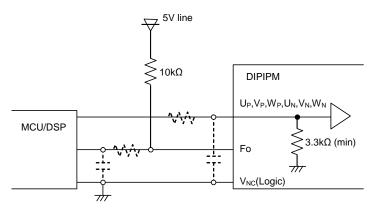

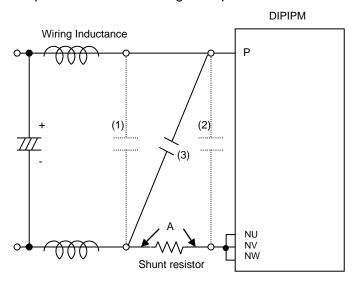

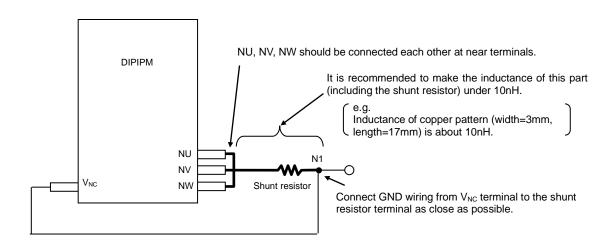

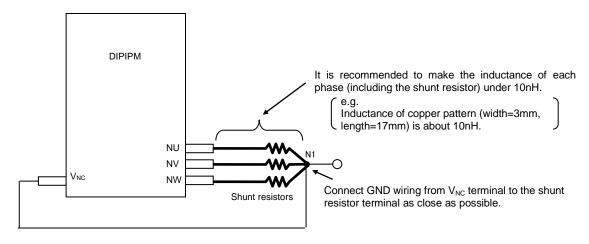

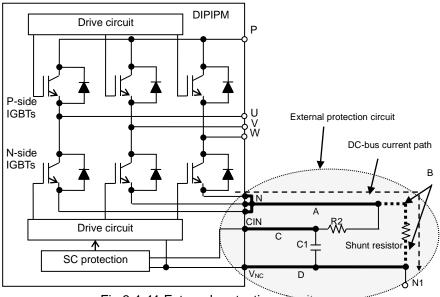

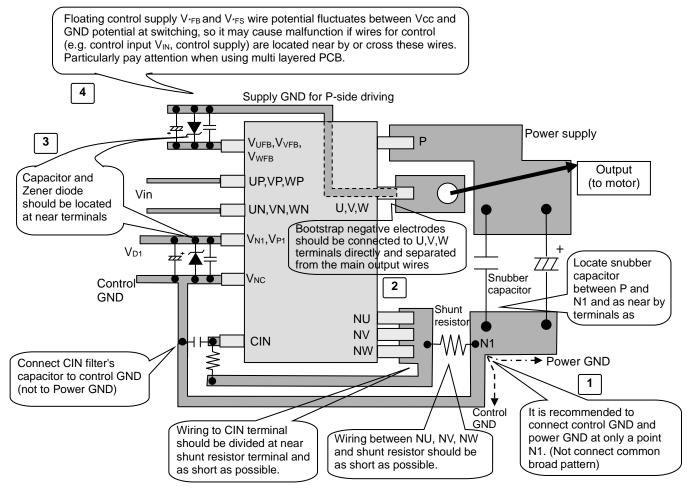

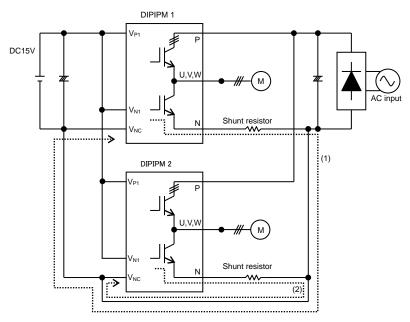

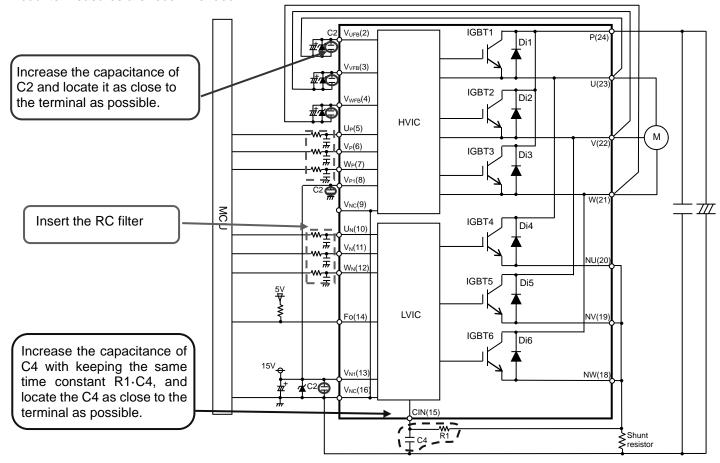

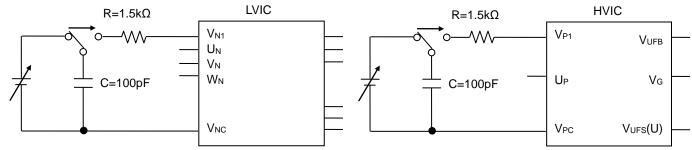

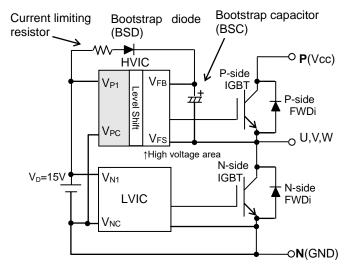

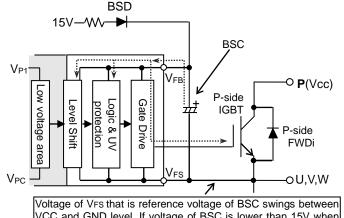

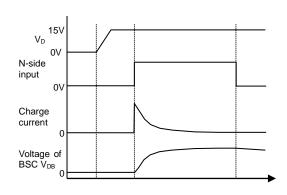

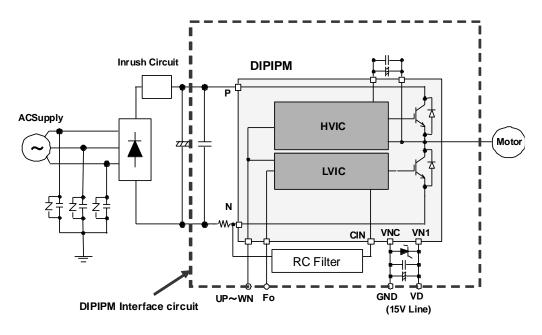

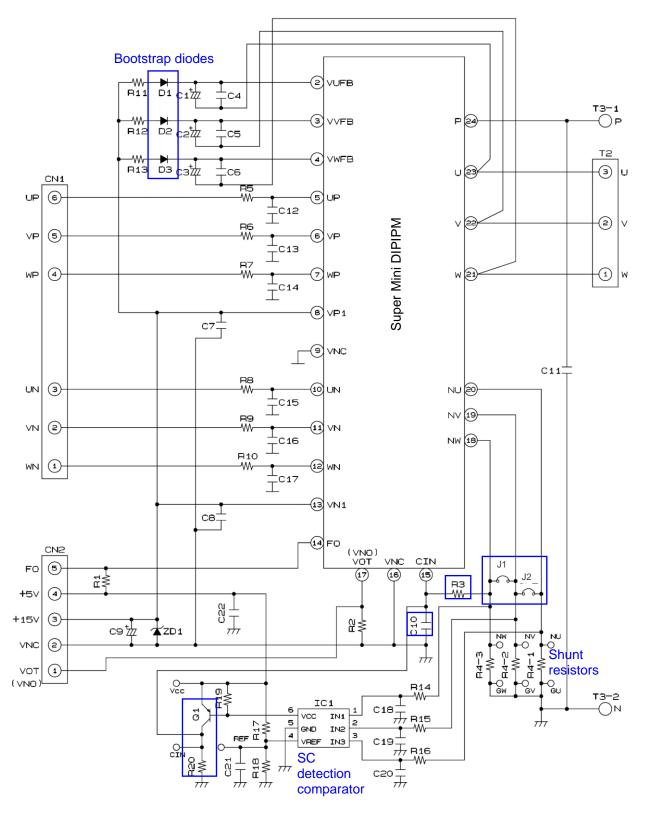

Note 1: Plain washers (ISO 7089~7094) are recommended.